Radio logicielle

I.Introduction

La radio logicielle (Software Defined Radio) est sous forme d'un récepteur câblé (Hardware) qui consiste à numériser le signal d'entrée et à le traiter par logiciel pour avoir les possibilités d'évolution, que ce soit en terme de fréquence qu'en terme de modulation, et pour assurer une vitesse de traitement suffisante en implémentant les algorithmes sur FPGA en VHDL. Dans ce projet, on focalisera l'étude sur les signaux de l'horloge atomique DCF (77,5kHz) en utilisant un convertisseur analogique numérique afin de pouvoir utiliser le FPGA.

Les radios logicielles sont par exemple utilisées dans les réseaux radio-mobiles (GSM, UMTS, etc.) au niveau des stations de base. Elles présentent les avantages suivants :

possibilité d'émettre (et de recevoir) des signaux simultanément dans plusieurs canaux, à l'aide d'un unique émetteur/récepteur

performances accrues en réception par rapport à des technologies radio traditionnelles

possibilité de mettre à jour logiciellement les BTS pour supporter de nouvelles modulations (exemple : migration de la norme GSM à la norme EDGE)

II.Avancement du projet

1ère séance

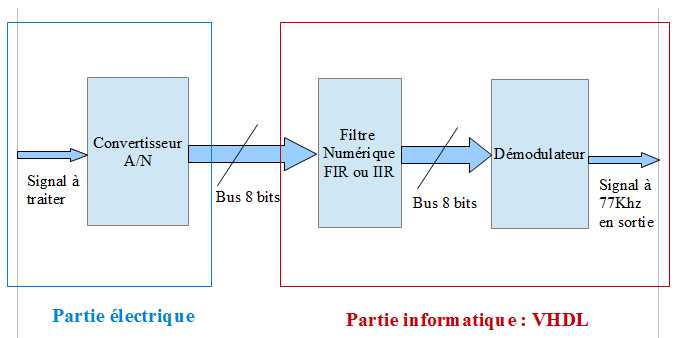

Dans un premier temps, on a essayé de comprendre le principe du fonctionnement du SDR (Radio Logicielle) en discutant avec les professeurs référents Alexandre Boé et Nicolas Defrance. Nous avons donc pu dans un premier temps distinguer deux parties dominantes dans ce projet :

-Une partie électronique (réalisation du convertisseur analogique/numérique).

-Une partie informatique (réalisation d'un code en VHDL permettant le filtrage à 77,5Khz du signal reçu et la démodulation de ce signal filtré).

Ainsi nous avons établi dans un premier temps un schéma du principe de fonctionnement de ce projet qui contient un convertisseur analogique-numérique, un filtre numérique et un démodulateur analogique.

2ème séance

Notre principal objectif est de recevoir un signal analogique et le convertir en numérique pour le traiter ( filtrer et démoduler )et il doit être adéquat à la bande de fréquences dont on a besoin, c'est à dire choisir les bons coefficients pour pouvoir les introduire dans le VHDL, et on a choisi de travailler sur un filtre FIR (filtre à réponse impulsionnelle finie) au lieu d'un filtre IIR (filtre à réponse impulsionnelle infinie) car le FIR est un filtre non récursif, il est stable peu importe les coefficients utilisés et il est moins sensible aux erreurs de quantification que les filtres IIR. Ensuite, on a réussi à trouver ces coefficients pour avoir la bande de fréquence voulue à l'aide de FDATOOL (MATLAB).

3ème et 4ème séance

Afin de comprendre au mieux les différents éléments constituant notre travail, nous nous sommes intéressés au signal d'entrée et au signal recherché. Le signal recherché correspond au signal DCF77 qui a pour fréquence porteuse une fréquence de 77,5Khz. Nous avons donc commencé à chercher une antenne de fréquences d'utilisation pouvant contenir notre signal DCF77. Après s'être renseigné auprès des professeurs à la recherche d'un telle antenne, plusieurs antennes étaient disponibles dans l'école et nous avons donc opté pour une antenne radioélectrique captant des ondes électromagnétiques de fréquences allant jusqu'à 1 Mhz et contenant donc notre signal DCF77. Les champs électriques des ondes électromagnétiques captés pouvant induire une tension aux bornes d'une antenne; nous avons donc effectué quelques tests avec cette antenne afin d'évaluer la plage de tension que pouvait fournir l'antenne. A l'aide d'un oscilloscope, nous avons mesuré ces tensions et nous sommes rendu compte que notre antenne ne délivrait que des tensions de l'ordre du milli-volt.

5ème séance

---

Dans un premier temps, nous avons cherché une façon de réaliser une carte de conversion Analogique/numérique à base de composants existants.

Nous nous sommes d'abord posé la question du type de convertisseur que l'on pouvait réaliser.

Nous nous sommes donc intéressé aux différents types de convertisseurs existants.

Les signaux à convertir étant des signaux audio d'assez hautes fréquences, il était nécessaire de trouver un convertisseur assez rapide capable d'effectuer la conversion.

Parmi les différents types de convertisseurs, ceux de type « convertisseurs à approximations successives » et ceux de type « convertisseurs flash » ou « semi-flash pipeline » convenaient très bien pour notre application étant donné leur grande vitesse de conversion contrairement aux convertisseurs à simple et double rampe qui sont des convertisseurs très précis mais très lents.

Les convertisseurs flash ou semi-flash ont la particularité d'être des convertisseurs très rapides mais très chers, utilisés principalement pour des applications critiques comme la vidéo, alors que les convertisseurs à approximations successives ont des temps de conversions de l'ordre de la dizaine de microsecondes pour des résolutions allant jusqu'à la douzaine de bits et sont moins chers. Ces convertisseurs à approximations successives sont donc plutôt utilisés dans le domaine de l'audio.

Nous avons donc choisit de travailler avec un convertisseur à approximations successives qui représentent les meilleurs rapports vitesse de conversion/prix et vitesse de conversion/précision.

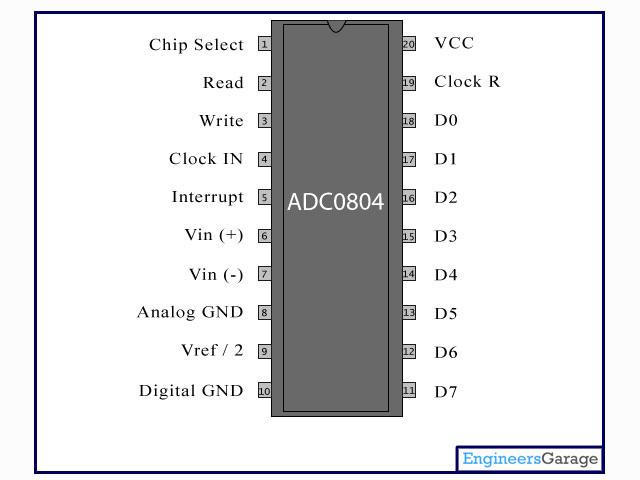

Nous avons ainsi cherché sur différents sites de fabricants de circuits intégrés des convertisseurs analogiques/numériques à approximations successives, et après en avoir demandé conseil auprès des professeurs référents devant la multitudes de composants CAN correspondants à nos critères (convertisseurs 8bits à haute vitesse de conversion) disponibles sur le site de chez Maxim, les professeurs nous ont proposé un convertisseur déjà disponible dans la salle de TP et tout à fait approprié pour notre projet (ADC0804LCN).

Nous avions donc quelques convertisseurs ADC 0804 à notre disposition.

6ème séance

A l'aide d'un ADC0804LCN 8 bits qui nous à été fourni, nous avons donc cherché a fabriquer cette carte. Après quelques recherches, à l'aide de résistances, de condensateurs, d'un potentiomètre, nous nous sommes rendu compte que ce convertisseur ne convertit que les valeurs reçus entre 0V et 5V et nous avons conçu une première carte de conversion. En réalisant un premier montage, nous avons constaté que ca fonctionnait pas.

7ème séance

Nous avons trouvé que le dysfonctionnement du convertisseur qu'on a réalisé était dû à un problème de contact. Le montage électronique qu'on a établit permet alors de recevoir des signaux de 0V à 5V et de les convertir en signaux numériques de 8 bits. Et puis, on a essayé de voir comment on peut adapter un signal venant de l'antenne (-5V à 5V) à l'entrée du convertisseur qui accepte que des signaux de 0V à 5V.

8ème et 9ème séance

Afin de convertir les valeurs du signal qui varient entre -5V et 5V (Antenne), on a décidé de mettre 2 amplificateurs opérationnels (le premier est un diviseur, le deuxième est un inverseur) en aval du convertisseur qui accepte que des valeurs entre 0V à 5V. Pour le filtre numérique, on a calculé d'une autre façon les coefficients qui nous permettront d'avoir un filtre passe bande qui laisse passer la fréquence de 77,5Khz grâce à Scilab. En outre, on a introduit ces coefficients dans le VHDL qui consiste à faire les opérations mathématiques pour un bloc du filtre numérique sachant qu'il y a n blocs du FIR (où n est l'ordre de ce filtre). Et puis, on a convertit ces coefficients en binaire (8 bits) pour que le FPGA puisse les reconnaître (en utilisant conv_std_logic).

10ème séance

On a réalisé le code VHDL du premier bloc qui consiste à multiplier le coefficient par le signal d'entrée et à sommer ce résultat avec le signal antécédent en prenant en compte le retard entre chaque bloc du filtre (delay) : y[n] = sum(Bk.x[n-k]) pour k allant de 0 à N (N:ordre du filtre) où y[i] représente les valeurs du signal de sortie, x[i] représente les valeurs du signal d'entrée et Bi représente les coefficients du filtre numérique.

11ème séance

On a réalisé le code VHDL de la deuxième partie qui consiste à traiter tous les blocs du filtre numérique en introduisant les coefficients du filtre et en utilisant le premier code du VHDL. En exécutant les 2 codes du VHDL, il n'y avait aucune erreur affichée. Mais lors de la visualisation sur l'écran, on obtenait des signaux aléatoires et non pas le signal qu'on comptait avoir. Cela peut être dû aux coefficients du filtre puisque le fonctionnement est très sensible à ces derniers.

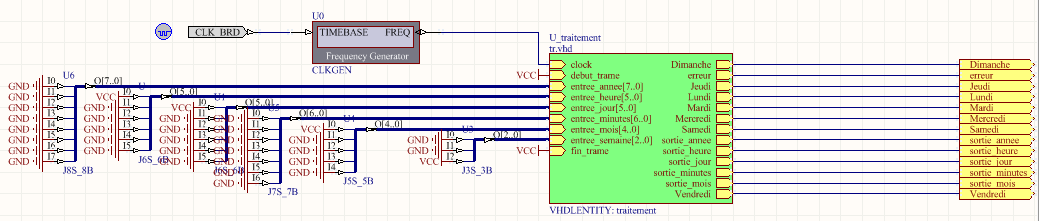

12ème et 13ème séance

On a établit 2 codes vhdl dont l'un consiste à identifier les bits (0 ou 1) selon les durées d'impulsions, et l'autre consiste à décoder le signal de 8 bits et qui est codé en BCD.