Modem pour le numérique : Différence entre versions

(→Modulateur et démodulateur pour communications numériques) |

(→Modulateur et démodulateur pour communications numériques) |

||

| Ligne 13 : | Ligne 13 : | ||

-pour la TNT en 64 QAM (en France). | -pour la TNT en 64 QAM (en France). | ||

| − | [[Fichier:P34_2013_2014_64qam.jpg | + | [[Fichier:P34_2013_2014_64qam.jpg]] |

-pour le WiFi en 64-QAM ou 256-QAM (à vérifier). | -pour le WiFi en 64-QAM ou 256-QAM (à vérifier). | ||

| Ligne 166 : | Ligne 166 : | ||

On aura bien pour une QPSK (4PSK) tous les couples (ie 00,01,11 et 10). | On aura bien pour une QPSK (4PSK) tous les couples (ie 00,01,11 et 10). | ||

| + | |||

| + | = Modulateur et démodulateur pour communications numériques = | ||

| + | |||

| + | == Cahier des charges == | ||

| + | |||

| + | === Présentation générale du projet === | ||

| + | |||

| + | Dans le cadre des TPs d'électronique et de transmission RF, nous avons découvert qu'il existe plusieurs modes de modulation, pour transmettre un signal modulant. | ||

| + | |||

| + | Celles vues en TP au S7 sont la modulation en amplitude, en fréquence, en phase, en BPSK et en QPSK. | ||

| + | |||

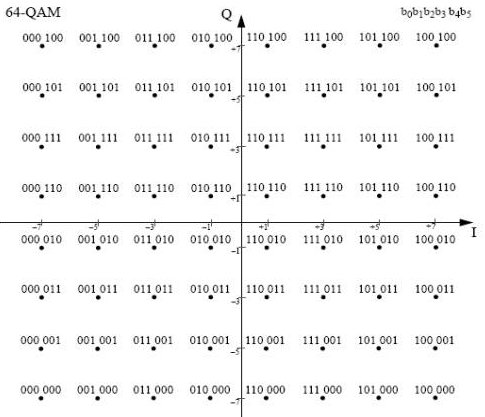

| + | Or les modulations en phase, en fréquence et en amplitude étant celles les plus connues, la modulation en QAM (Modulation d'Amplitude en Quadrature) est quant à elle moins connue, mais tout aussi utilisées: | ||

| + | |||

| + | -pour la TNT en 64 QAM (en France). | ||

| + | |||

| + | [[Fichier:P34_2013_2014_64qam.jpg]] | ||

| + | |||

| + | -pour le WiFi en 64-QAM ou 256-QAM (à vérifier). | ||

| + | |||

| + | Or ces deux dernières étant peu représentées au niveau des travaux pratiques, ce projet permettra de fournir un peu plus de pratique sur les modulations de type QAM (en diagramme I/Q) dans le domaine des radiofréquences (~800MHz). | ||

| + | |||

| + | (Le nombre devant le QAM indique le nombre de points dans le diagramme I/Q qu'on appelle aussi constellation) | ||

| + | |||

| + | |||

| + | On se réserve le droit de faire '''évoluer''' le cahier des charges a posteriori, si certaines contraintes étaient amenées à évoluer ou se préciser. | ||

| + | |||

| + | === Objectif et intérêt du projet === | ||

| + | |||

| + | Pour cela, on nous a fourni des modules commerciaux Mini-circuit pouvant travailler dans les radios-fréquences. | ||

| + | |||

| + | Ceux-ci permettront de mettre en place une grande partie de la chaine de transmission (voir schéma de la chaine de transmission). | ||

| + | |||

| + | [[Fichier:P34_2013_2014_Chaine_modulation.PNG|300px|thumb|center|Modulation.]] | ||

| + | |||

| + | [[Fichier:P34_2013_2014_Chaine_demodulation.PNG?|300px|thumb|center|Demodulation.]] | ||

| + | |||

| + | On a tout d'abord à mettre en place une carte FPGA et/ou un dispositif permettant d'envoyer un flux de données numériques continuellement pour pouvoir visualiser le diagramme I/Q (mise en valeur du diagramme I/Q et voir même un diagramme un peu plus complexe que le BPSK ou le QPSK). | ||

| + | |||

| + | Le canal de transmission qui sera un simple fil électrique, mais pourra devenir une antenne réceptrice et émettrice si le temps imparti le permet (mise en valeur du et mesure du Bit Error Rate qui sera bien sûr différent suivant le canal de transmission). | ||

| + | |||

| + | Du côté réception ,après démodulation du signal, une remise en forme et une interprétation des données seront réalisées, celle-ci dépendra bien entendu de la provenance du flux de données (constater le succès ou l'échec d'un envoi de données). | ||

| + | |||

| + | Enfin si le temps le permets on pourra mettre en une place un système de codage de l'information avec par exemple un codage redondant permettant de corrigé l'erreur (À définir, on pourra faire constater l'efficacité d'une méthode de codage au choix). | ||

| + | |||

| + | === Étapes/Déroulement du projet === | ||

| + | |||

| + | De même que pour le cahier des charges, il se peut que les étapes diffèrent plus ou moins, en fonction des disponibilités, matérielles et contraintes. | ||

| + | |||

| + | ==== => Caractérisation des blocs Mini-circuits et épluchage des documentations techniques==== | ||

| + | Avant de les utiliser dans la chaine de transmission, nous avons à faire une caractérisation des blocs fournis: | ||

| + | |||

| + | -la caractérisation du VCO. | ||

| + | |||

| + | -l'étude des possibilités offerte par le modulateur (cela déterminera le nombre de points possible dans la constellation, ie savoir si l'on peut aller au-delà de la QPSK). | ||

| + | |||

| + | -la caractérisation des mélangeurs (Mixer), leurs facteurs réels de multiplication. | ||

| + | |||

| + | ==== => Utilisation et exploitation des caractérisations ==== | ||

| + | On pourra ensuite trouver les paramètres pour régler correctement dans notre chaine de transmission certains de nos sous-systèmes comme la boucle à verrouillage de phase. | ||

| + | |||

| + | ==== => Génération d'un flux des données numériques ==== | ||

| + | Comme dit précédemment, l'idéal et d'avoir un flux de données numériques transmis en permanence. | ||

| + | Pour cela plusieurs solutions s'offre à nous, on pourra utiliser un montage générateur pseudo aléatoire (un circuit que l'on a fait l'année dernière en Conception de Circuit Électronique). | ||

| + | On pourra "émuler" ce montage avec un Arduino, ou bien même le faire au moyen de la Nanoboard. | ||

| + | On pourra aussi transmettre des chaines de caractère en continu. | ||

| + | |||

| + | ==== => Test de la chaine ==== | ||

| + | Une fois les étapes précédentes réalisées, on pourra passer au test de la chaine de transmission. Il faudra vérifier le bon fonctionnement en aval, dedans (boucle a verrouillage de phase), et en amont de la chaine de transmission. | ||

| + | |||

| + | ==== => Première mesure du Bit Error Rate ==== | ||

| + | Il sera temps de mesurer/déterminer le B.E.R. de la chaine de transmission avec un fil électrique en tant que canal de transmission. | ||

| + | Il est possible que la conception d'un dispositif soit nécessaire que ce soit pour les deux mesures du B.E.R.. | ||

| + | |||

| + | ==== => Antennes ==== | ||

| + | Si toutes les étapes précédentes sont satisfaites, on pourra alors faire un canal de transmission plus intéressant, à savoir l'air. | ||

| + | Nous passerons alors à la conception des antennes, émettrice et réceptrice. | ||

| + | |||

| + | ==== => Deuxième mesure du Bit Error Rate ==== | ||

| + | Il sera temps de mesurer/déterminer le B.E.R. de la chaine de transmission avec un fil électrique en tant que canal de transmission. | ||

| + | |||

| + | ==== => Codage de l'information et correction d'erreur ==== | ||

| + | En toute fin de ce projet, on pourra même mettre deux dispositifs en aval et en amont de la chaine de transmission. | ||

| + | On réalisera alors un codeur et un décodeur permettant de faire de la détection/correction d'erreur. | ||

| + | |||

| + | ==== => Mise en place d'outil de débogage (tout au long)==== | ||

| + | La mise en place de simples outils de débogage et primordiale, ceux-ci permettront de vérifier le bon fonctionnement de la chaine. | ||

| + | |||

| + | ==== => Proposition d'un sujet de TP (tout au long) ==== | ||

| + | Il se trouve que lors du déroulement du projet, on pourra être amené à se poser des questions au niveau des réglages de la chaine de transmission. | ||

| + | Or il est fort probable que les élèves qui travailleront sur ce TP pourront alors se poser les mêmes questions. | ||

| + | C'est pour cela qui sera judicieux de prendre soin de noter les problématiques rencontrées et de donner un certain fil de développement pour venir à bout de la problématique posée. | ||

| + | Ce qui reviendra à proposer des axes/questions sur les manipulations de cette maquette de TP. | ||

| + | |||

| + | == Séance du 05/02/2014 (Rédaction en cours): == | ||

| + | |||

| + | Pour bien comprendre les différentes choses à réaliser, on a refait les manipulations vues en TP. On a, pour cela utiliser la maquette didactique TIMS pour générer différent type de modulation: | ||

| + | |||

| + | -la modulation en 4,8,16PSK (on obtient une constellation en forme de cercle). | ||

| + | |||

| + | -La modulation en 4,8,16QAM (on obtient une constellation avec un carré, ou deux: de différentes tailles). | ||

| + | |||

| + | On a très vite dégagé la nécessité de réaliser un montage générateur de tous les mots numériques possibles. | ||

| + | On a donc fait un programme sur arduino qui équivaut au générateur pseudo aléatoire. | ||

| + | Celui-ci est directement inspiré du montage que l'on a réalisé l'année dernière en conception de circuit électronique. | ||

| + | Voir la section "Code Arduino réalisé". | ||

| + | |||

| + | |||

| + | Après on a réfléchi sur la potentielle conception d'une carte FPGA. | ||

| + | Il sera judicieux de ne pas se précipiter sur le schéma et la conception de la carte FPGA, sans avoir, au préalable fait le VHDL et le testez avec un banc de test virtuel. | ||

| + | L'intérêt et de mettre en valeur la nécessité ou non de certains signaux pour le schéma de la carte. | ||

| + | On va mettre en oeuvre les connaissances acquises au S7 en VHDL (en TP de Circuit Numérique Programmble). | ||

| + | |||

| + | |||

| + | Pour ce qui est de l'Arduino, on a répondu aux interrogations suivantes (certaines de ces questions paraissent triviales, mais on préfère éviter les surprises): | ||

| + | |||

| + | Quelle est la vitesse maximale de la communication série de l'Arduino ? | ||

| + | -115200bauds | ||

| + | |||

| + | Est-ce que, un programme de type "Analog Write" est-il une vraie sortie analogique ? | ||

| + | |||

| + | -Non, c'est juste une PWM. Elle sera exploitable pour faire les signales I/Q mais très contraignantes, car il faudra filtré le signal, et ce sera beaucoup trop lent (du au fait que la modulation est faite au alentour de 850Mhz), le FPGA sera un passage obligé cela ouvrira les portes d'un plus grand débit. | ||

| + | |||

| + | |||

| + | === Code Arduino réalisé: === | ||

| + | |||

| + | [[Fichier:P34_2013_2014_schema_electronique_generateur_pseudo_aleatoire.png??|300px|thumb|center|Schéma électronique du générateur pseudo aléatoire.]] | ||

| + | |||

| + | [[Fichier:P34_2013_2014_generateur_pseudo_aleatoire_chrono_simule.PNG?|300px|thumb|center|Résultat de la simulation du générateur pseudo aléatoire (on a eu la même chose en pratique).]] | ||

| + | |||

| + | [code] | ||

| + | /*A peut être supprimer*/ | ||

| + | #include <avr/io.h> | ||

| + | #include <util/delay.h> | ||

| + | |||

| + | void output_init(void){ | ||

| + | DDRB |= 0x02; // PIN 8,9 sont les deux sorties. | ||

| + | } | ||

| + | |||

| + | int main(void){ | ||

| + | int r1=1,r2=0,r3=0,r4=0,r5=0,retard=0; | ||

| + | PORTB=0x00; | ||

| + | while(1) | ||

| + | { | ||

| + | r5=r4;//chaque affectation représente une recopie de la bascule sur le "front montant", ici c'est simplement l’exécution du code. | ||

| + | r4=r3; | ||

| + | r3=r2; | ||

| + | r2=r1; | ||

| + | r1=r4^r5; | ||

| + | PORTB=0x01*r1+0x02*retard;//écriture des signaux | ||

| + | _delay_ms(10);//le "front montant", ce qui permet de faire un genre d'horloge. | ||

| + | retard=r5;//déphasage du signal | ||

| + | } | ||

| + | return 0; | ||

| + | } | ||

| + | [/code] | ||

| + | |||

| + | [[Fichier:P34_2013_2014_generateur_pseudo_aleatoire_arduino.jpg|300px|thumb|center|Resultat avec le generateur pseudo aléatoire "émuler" avec l'Arduino.]] | ||

| + | |||

| + | Comparaison carte réelle/résultat Arduino: | ||

| + | |||

| + | C'était exactement les signaux attendus (même s'il y un décalage a par rapport à l'original). | ||

| + | |||

| + | On aura bien pour une QPSK (4PSK) tous les couples (ie 00,01,11 et 10). | ||

| + | |||

| + | |||

| + | === Séance du 06/02/2014 (Rédaction en cours): === | ||

| + | |||

| + | À propos de l'arduino, on pourra envisager une amélioration pour générer une séquence plus longue: | ||

| + | |||

| + | -il faudra simplement utiliser un tableau d'entier. | ||

| + | |||

| + | -paramétrer sa taille avec un N par exemple. | ||

| + | |||

| + | -N correspondra à la taille de séquence de longueur 2^N. | ||

| + | |||

| + | |||

| + | ==== Possibilités de communications: ==== | ||

| + | |||

| + | Exploration des possibilités de communication entre le PC et la carte en amont: | ||

| + | |||

| + | ======-> Ethernet: ===== | ||

| + | |||

| + | *+ Vitesse de transmission (~10M-100M-G)bauds | ||

| + | |||

| + | *- La gestion du flux de données doit être faite par un microcontrôleur (celui-ci pourra être implémenté un bloc I.P. à l'intérieur du FPGA) | ||

| + | |||

| + | -> - Haute consommation de CLB du FPGA. | ||

| + | |||

| + | =====-> SPI (communication série): ===== | ||

| + | |||

| + | *- Vitesse de transmission | ||

| + | |||

| + | -> Arduino capable jusqu'a 115200 bauds | ||

| + | |||

| + | -> D'après certaines discussions on pourrait « pousser » au-delà : voir le lien des sujets Raspberry Pi. | ||

| + | |||

| + | =====-> I2C (recherche à faire): ===== | ||

| + | |||

| + | Communication abandonné, ce n'est pas une priorité. | ||

| + | |||

| + | |||

| + | ==== À propos des blocs I.P.: ==== | ||

| + | |||

| + | En consultant les ordinateurs et en s'appuyant des TPs de CNP, on constate que les blocs suivants existent: | ||

| + | |||

| + | - Xilinx Microblaze/Xilinx Power PC ("µP FPGA") | ||

| + | |||

| + | -> Est-ce possible d'utiliser ces blocs I.P. pour programmer un FPGA sur une carte autre que la Nanoboard ? Comment ? | ||

| + | |||

| + | - EMACx (Ethernet Media Acess Control)(:lien physique entre processeurs et « standart Physical Layer device IEEE802.3) | ||

| + | |||

| + | ==== Conception de la carte: ==== | ||

| + | |||

| + | L'idéal est de se documenter sur la Compatibilité électromagnétique. | ||

| + | |||

| + | == 2éme semaine: (rédaction en cours) (du 03/02/2014 08/02/2014) == | ||

| + | |||

| + | == 3éme semaine: (rédaction en cours) (du 10/02/2014 15/02/2014) == | ||

| + | |||

| + | == 4éme semaine: (rédaction en cours) (du 17/02/2014 22/02/2014) == | ||

| + | |||

| + | == 5éme semaine: (rédaction en cours) (du 03/03/2014 08/03/2014) == | ||

| + | |||

| + | == 6éme semaine: (rédaction en cours) (du 10/03/2014 15/03/2014) == | ||

| + | |||

| + | == 7éme semaine: (rédaction en cours) (du 17/03/2014 22/03/2014) == | ||

| + | |||

| + | |||

| + | === Pour les prochaines séances: === | ||

| + | |||

| + | Une évaluation du nombre de bits du CAN sera appréciable, il faudrais s'appuyer d'un diagramme des constellations et des tolérances sur l'appertenance des points a un mot. | ||

| + | |||

| + | Pour les manipulations: | ||

| + | |||

| + | On fera la manipulation le 10/02/14 pour tester la chaine composée des composants Minicircuit. | ||

| + | |||

| + | === Questions en suspend et idées(Rédaction en cours): === | ||

| + | |||

| + | -Comment programmer un FPGA: in situe, ISE Xilinx, matériel requis, programmeur JTAG, | ||

| + | |||

| + | -Communications entre arduinos (en fin de projet) via la chaine | ||

| + | |||

| + | -iInterface USB | ||

= Modulateur et démodulateur pour communications numériques = | = Modulateur et démodulateur pour communications numériques = | ||

Version du 23 mars 2014 à 11:06

Sommaire

- 1 Modulateur et démodulateur pour communications numériques

- 1.1 Cahier des charges (en cours de rédaction)

- 1.1.1 Présentation générale du projet

- 1.1.2 Objectif et intérêt du projet

- 1.1.3 Étapes/Déroulement du projet

- 1.1.3.1 => Caractérisation des blocs Mini-circuits et épluchage des documentations techniques

- 1.1.3.2 => Utilisation et exploitation des caractérisations

- 1.1.3.3 => Génération d'un flux des données numériques

- 1.1.3.4 => Test de la chaine

- 1.1.3.5 => Première mesure du Bit Error Rate

- 1.1.3.6 => Antennes

- 1.1.3.7 => Deuxième mesure du Bit Error Rate

- 1.1.3.8 => Codage de l'information et correction d'erreur

- 1.1.3.9 => Mise en place d'outil de débogage (tout au long)

- 1.1.3.10 => Proposition d'un sujet de TP (tout au long)

- 1.2 1ére Semaine 06/02/2014

- 1.1 Cahier des charges (en cours de rédaction)

- 2 Modulateur et démodulateur pour communications numériques

- 2.1 Cahier des charges

- 2.1.1 Présentation générale du projet

- 2.1.2 Objectif et intérêt du projet

- 2.1.3 Étapes/Déroulement du projet

- 2.1.3.1 => Caractérisation des blocs Mini-circuits et épluchage des documentations techniques

- 2.1.3.2 => Utilisation et exploitation des caractérisations

- 2.1.3.3 => Génération d'un flux des données numériques

- 2.1.3.4 => Test de la chaine

- 2.1.3.5 => Première mesure du Bit Error Rate

- 2.1.3.6 => Antennes

- 2.1.3.7 => Deuxième mesure du Bit Error Rate

- 2.1.3.8 => Codage de l'information et correction d'erreur

- 2.1.3.9 => Mise en place d'outil de débogage (tout au long)

- 2.1.3.10 => Proposition d'un sujet de TP (tout au long)

- 2.2 Séance du 05/02/2014 (Rédaction en cours):

- 2.3 2éme semaine: (rédaction en cours) (du 03/02/2014 08/02/2014)

- 2.4 3éme semaine: (rédaction en cours) (du 10/02/2014 15/02/2014)

- 2.5 4éme semaine: (rédaction en cours) (du 17/02/2014 22/02/2014)

- 2.6 5éme semaine: (rédaction en cours) (du 03/03/2014 08/03/2014)

- 2.7 6éme semaine: (rédaction en cours) (du 10/03/2014 15/03/2014)

- 2.8 7éme semaine: (rédaction en cours) (du 17/03/2014 22/03/2014)

- 2.1 Cahier des charges

- 3 Modulateur et démodulateur pour communications numériques

- 3.1 Cahier des charges

- 3.1.1 Présentation générale du projet

- 3.1.2 Objectif et intérêt du projet

- 3.1.3 Étapes/Déroulement du projet

- 3.1.3.1 => Caractérisation des blocs Mini-circuits et épluchage des documentations techniques

- 3.1.3.2 => Utilisation et exploitation des caractérisations

- 3.1.3.3 => Génération d'un flux des données numériques

- 3.1.3.4 => Test de la chaine

- 3.1.3.5 => Première mesure du Bit Error Rate

- 3.1.3.6 => Antennes

- 3.1.3.7 => Deuxième mesure du Bit Error Rate

- 3.1.3.8 => Codage de l'information et correction d'erreur

- 3.1.3.9 => Mise en place d'outil de débogage (tout au long)

- 3.1.3.10 => Proposition d'un sujet de TP (tout au long)

- 3.2 Séance du 05/02/2014 (Rédaction en cours):

- 3.3 2éme semaine: (rédaction en cours) (du 03/02/2014 08/02/2014)

- 3.4 3éme semaine: (rédaction en cours) (du 10/02/2014 15/02/2014)

- 3.5 4éme semaine: (rédaction en cours) (du 17/02/2014 22/02/2014)

- 3.6 5éme semaine: (rédaction en cours) (du 03/03/2014 08/03/2014)

- 3.7 6éme semaine: (rédaction en cours) (du 10/03/2014 15/03/2014)

- 3.8 7éme semaine: (rédaction en cours) (du 17/03/2014 22/03/2014)

- 3.1 Cahier des charges

Modulateur et démodulateur pour communications numériques

Cahier des charges (en cours de rédaction)

Présentation générale du projet

Dans le cadre des TPs d'électronique et de transmission RF, nous avons découvert qu'il existe plusieurs modes de modulation, pour transmettre un signal modulant.

Celles vues en TP au S7 sont la modulation en amplitude, en fréquence, en phase, en BPSK et en QPSK.

Or les modulations en phase, en fréquence et en amplitude étant celles les plus connues, la modulation en QAM (Modulation d'Amplitude en Quadrature) est quant à elle moins connue, mais tout aussi utilisées:

-pour la TNT en 64 QAM (en France).

-pour le WiFi en 64-QAM ou 256-QAM (à vérifier).

Or ces deux dernières étant peu représentées au niveau des travaux pratiques, ce projet permettra de fournir un peu plus de pratique sur les modulations de type QAM (en diagramme I/Q) dans le domaine des radiofréquences (~800MHz).

(Le nombre devant le QAM indique le nombre de points dans le diagramme I/Q qu'on appelle aussi constellation)

On se réserve le droit de faire évoluer le cahier des charges a posteriori, si certaines contraintes étaient amenées à évoluer ou se préciser.

Objectif et intérêt du projet

Pour cela, on nous a fourni des modules commerciaux Mini-circuit pouvant travailler dans les radios-fréquences.

Ceux-ci permettront de mettre en place une grande partie de la chaine de transmission (voir schéma de la chaine de transmission).

On a tout d'abord à mettre en place une carte FPGA et/ou un dispositif permettant d'envoyer un flux de données numériques continuellement pour pouvoir visualiser le diagramme I/Q (mise en valeur du diagramme I/Q et voir même un diagramme un peu plus complexe que le BPSK ou le QPSK).

Le canal de transmission qui sera un simple fil électrique, mais pourra devenir une antenne réceptrice et émettrice si le temps imparti le permet (mise en valeur du et mesure du Bit Error Rate qui sera bien sûr différent suivant le canal de transmission).

Du côté réception ,après démodulation du signal, une remise en forme et une interprétation des données seront réalisées, celle-ci dépendra bien entendu de la provenance du flux de données (constater le succès ou l'échec d'un envoi de données).

Enfin si le temps le permets on pourra mettre en une place un système de codage de l'information avec par exemple un codage redondant permettant de corrigé l'erreur (À définir, on pourra faire constater l'efficacité d'une méthode de codage au choix).

Étapes/Déroulement du projet

De même que pour le cahier des charges, il se peut que les étapes diffèrent plus ou moins, en fonction des disponibilités, matérielles et contraintes.

=> Caractérisation des blocs Mini-circuits et épluchage des documentations techniques

Avant de les utiliser dans la chaine de transmission, nous avons à faire une caractérisation des blocs fournis:

-la caractérisation du VCO.

-l'étude des possibilités offerte par le modulateur (cela déterminera le nombre de points possible dans la constellation, ie savoir si l'on peut aller au-delà de la QPSK).

-la caractérisation des mélangeurs (Mixer), leurs facteurs réels de multiplication.

=> Utilisation et exploitation des caractérisations

On pourra ensuite trouver les paramètres pour régler correctement dans notre chaine de transmission certains de nos sous-systèmes comme la boucle à verrouillage de phase.

=> Génération d'un flux des données numériques

Comme dit précédemment, l'idéal et d'avoir un flux de données numériques transmis en permanence. Pour cela plusieurs solutions s'offre à nous, on pourra utiliser un montage générateur pseudo aléatoire (un circuit que l'on a fait l'année dernière en Conception de Circuit Électronique). On pourra « émuler » ce montage avec un Arduino, ou bien même le faire au moyen de la Nanoboard. On pourra aussi transmettre des chaines de caractère en continu.

=> Test de la chaine

Une fois les étapes précédentes réalisées, on pourra passer au test de la chaine de transmission. Il faudra vérifier le bon fonctionnement en aval, dedans (boucle à verrouillage de phase), et en amont de la chaine de transmission.

=> Première mesure du Bit Error Rate

Il sera temps de mesurer/déterminer le B.E.R. de la chaine de transmission avec un fil électrique en tant que canal de transmission. Il est possible que la conception d'un dispositif soit nécessaire que ce soit pour les deux mesures du B.E.R..

=> Antennes

Si toutes les étapes précédentes sont satisfaites, on pourra alors faire un canal de transmission plus intéressant, à savoir l'air. Nous passerons alors à la conception des antennes, émettrice et réceptrice.

=> Deuxième mesure du Bit Error Rate

Il sera temps de mesurer/déterminer le B.E.R. de la chaine de transmission avec un fil électrique en tant que canal de transmission.

=> Codage de l'information et correction d'erreur

En toute fin de ce projet, on pourra même mettre deux dispositifs en aval et en amont de la chaine de transmission. On réalisera alors un codeur et un décodeur permettant de faire de la détection/correction d'erreur.

=> Mise en place d'outil de débogage (tout au long)

La mise en place de simples outils de débogage et primordiale, ceux-ci permettront de vérifier le bon fonctionnement de la chaine.

=> Proposition d'un sujet de TP (tout au long)

Il se trouve que lors du déroulement du projet, on pourra être amené à se poser des questions au niveau des réglages de la chaine de transmission. Or il est fort probable que les élèves qui travailleront sur ce TP pourront alors se poser les mêmes questions. C'est pour cela qui sera judicieux de prendre soin de noter les problématiques rencontrées et de donner un certain fil de développement pour venir à bout de la problématique posée. Ce qui reviendra à proposer des axes/questions sur les manipulations de cette maquette de TP.

1ére Semaine 06/02/2014

Séance du 03/02/2014 :

- Discussion avec les professeurs encadrants.

Séance du 05/02/2014 :

Pour bien comprendre les différentes choses à réaliser, on a refait les manipulations vues en TP. On a, pour cela utiliser la maquette didactique TIMS pour générer différent type de modulation:

-la modulation en 4,8,16PSK (on obtient une constellation en forme de cercle).

-La modulation en 4,8,16QAM (on obtient une constellation avec un carré, ou deux: de différentes tailles).

On a très vite dégagé la nécessité de réaliser un montage générateur de tous les mots numériques possibles. On a donc fait un programme sur arduino qui équivaut au générateur pseudo aléatoire. Celui-ci est directement inspiré du montage que l'on a réalisé l'année dernière en conception de circuit électronique. Voir la section « Code Arduino réalisé ».

Après on a réfléchi sur la potentielle conception d'une carte FPGA.

Il sera judicieux de ne pas se précipiter sur le schéma et la conception de la carte FPGA, sans avoir, au préalable fait le VHDL et le testez avec un banc de test virtuel.

L'intérêt et de mettre en valeur la nécessité ou non de certains signaux pour le schéma de la carte.

On va mettre en oeuvre les connaissances acquises au S7 en VHDL (en TP de Circuit Numérique Programmble).

Pour ce qui est de l'Arduino, on a répondu aux interrogations suivantes (certaines de ces questions paraissent triviales, mais on préfère éviter les surprises):

Quelle est la vitesse maximale de la communication série de l'Arduino ? -115200bauds

Est-ce que, un programme de type « Analog Write » est-il une vraie sortie analogique ?

-Non, c'est juste une PWM. Elle sera exploitable pour faire les signales I/Q mais très contraignantes, car il faudra filtré le signal, et ce sera beaucoup trop lent (du au fait que la modulation est faite au alentour de 850Mhz), le FPGA sera un passage obligé cela ouvrira les portes d'un plus grand débit.

Code Arduino réalisé:

[code] /*A peut-être supprimer*/

- include <avr/io.h>

- include <util/delay.h>

void output_init(void){

DDRB |= 0x02; // PIN 8,9 sont les deux sorties.

}

int main(void){

int r1=1,r2=0,r3=0,r4=0,r5=0,retard=0;

PORTB=0x00;

while(1)

{

r5=r4;//chaque affectation représente une recopie de la bascule sur le « front montant », ici c'est simplement l’exécution du code.

r4=r3;

r3=r2;

r2=r1;

r1=r4^r5;

PORTB=0x01*r1+0x02*retard;//écriture des signaux

_delay_ms(10);//le « front montant », ce qui permet de faire un genre d'horloge.

retard=r5;//déphasage du signal

}

return 0;

} [/code]

Comparaison carte réelle/résultat Arduino:

C'était exactement les signaux attendus (même s'il y un décalage a par rapport à l'original).

On aura bien pour une QPSK (4PSK) tous les couples (ie 00,01,11 et 10).

Modulateur et démodulateur pour communications numériques

Cahier des charges

Présentation générale du projet

Dans le cadre des TPs d'électronique et de transmission RF, nous avons découvert qu'il existe plusieurs modes de modulation, pour transmettre un signal modulant.

Celles vues en TP au S7 sont la modulation en amplitude, en fréquence, en phase, en BPSK et en QPSK.

Or les modulations en phase, en fréquence et en amplitude étant celles les plus connues, la modulation en QAM (Modulation d'Amplitude en Quadrature) est quant à elle moins connue, mais tout aussi utilisées:

-pour la TNT en 64 QAM (en France).

-pour le WiFi en 64-QAM ou 256-QAM (à vérifier).

Or ces deux dernières étant peu représentées au niveau des travaux pratiques, ce projet permettra de fournir un peu plus de pratique sur les modulations de type QAM (en diagramme I/Q) dans le domaine des radiofréquences (~800MHz).

(Le nombre devant le QAM indique le nombre de points dans le diagramme I/Q qu'on appelle aussi constellation)

On se réserve le droit de faire évoluer le cahier des charges a posteriori, si certaines contraintes étaient amenées à évoluer ou se préciser.

Objectif et intérêt du projet

Pour cela, on nous a fourni des modules commerciaux Mini-circuit pouvant travailler dans les radios-fréquences.

Ceux-ci permettront de mettre en place une grande partie de la chaine de transmission (voir schéma de la chaine de transmission).

On a tout d'abord à mettre en place une carte FPGA et/ou un dispositif permettant d'envoyer un flux de données numériques continuellement pour pouvoir visualiser le diagramme I/Q (mise en valeur du diagramme I/Q et voir même un diagramme un peu plus complexe que le BPSK ou le QPSK).

Le canal de transmission qui sera un simple fil électrique, mais pourra devenir une antenne réceptrice et émettrice si le temps imparti le permet (mise en valeur du et mesure du Bit Error Rate qui sera bien sûr différent suivant le canal de transmission).

Du côté réception ,après démodulation du signal, une remise en forme et une interprétation des données seront réalisées, celle-ci dépendra bien entendu de la provenance du flux de données (constater le succès ou l'échec d'un envoi de données).

Enfin si le temps le permets on pourra mettre en une place un système de codage de l'information avec par exemple un codage redondant permettant de corrigé l'erreur (À définir, on pourra faire constater l'efficacité d'une méthode de codage au choix).

Étapes/Déroulement du projet

De même que pour le cahier des charges, il se peut que les étapes diffèrent plus ou moins, en fonction des disponibilités, matérielles et contraintes.

=> Caractérisation des blocs Mini-circuits et épluchage des documentations techniques

Avant de les utiliser dans la chaine de transmission, nous avons à faire une caractérisation des blocs fournis:

-la caractérisation du VCO.

-l'étude des possibilités offerte par le modulateur (cela déterminera le nombre de points possible dans la constellation, ie savoir si l'on peut aller au-delà de la QPSK).

-la caractérisation des mélangeurs (Mixer), leurs facteurs réels de multiplication.

=> Utilisation et exploitation des caractérisations

On pourra ensuite trouver les paramètres pour régler correctement dans notre chaine de transmission certains de nos sous-systèmes comme la boucle à verrouillage de phase.

=> Génération d'un flux des données numériques

Comme dit précédemment, l'idéal et d'avoir un flux de données numériques transmis en permanence. Pour cela plusieurs solutions s'offre à nous, on pourra utiliser un montage générateur pseudo aléatoire (un circuit que l'on a fait l'année dernière en Conception de Circuit Électronique). On pourra "émuler" ce montage avec un Arduino, ou bien même le faire au moyen de la Nanoboard. On pourra aussi transmettre des chaines de caractère en continu.

=> Test de la chaine

Une fois les étapes précédentes réalisées, on pourra passer au test de la chaine de transmission. Il faudra vérifier le bon fonctionnement en aval, dedans (boucle a verrouillage de phase), et en amont de la chaine de transmission.

=> Première mesure du Bit Error Rate

Il sera temps de mesurer/déterminer le B.E.R. de la chaine de transmission avec un fil électrique en tant que canal de transmission. Il est possible que la conception d'un dispositif soit nécessaire que ce soit pour les deux mesures du B.E.R..

=> Antennes

Si toutes les étapes précédentes sont satisfaites, on pourra alors faire un canal de transmission plus intéressant, à savoir l'air. Nous passerons alors à la conception des antennes, émettrice et réceptrice.

=> Deuxième mesure du Bit Error Rate

Il sera temps de mesurer/déterminer le B.E.R. de la chaine de transmission avec un fil électrique en tant que canal de transmission.

=> Codage de l'information et correction d'erreur

En toute fin de ce projet, on pourra même mettre deux dispositifs en aval et en amont de la chaine de transmission. On réalisera alors un codeur et un décodeur permettant de faire de la détection/correction d'erreur.

=> Mise en place d'outil de débogage (tout au long)

La mise en place de simples outils de débogage et primordiale, ceux-ci permettront de vérifier le bon fonctionnement de la chaine.

=> Proposition d'un sujet de TP (tout au long)

Il se trouve que lors du déroulement du projet, on pourra être amené à se poser des questions au niveau des réglages de la chaine de transmission. Or il est fort probable que les élèves qui travailleront sur ce TP pourront alors se poser les mêmes questions. C'est pour cela qui sera judicieux de prendre soin de noter les problématiques rencontrées et de donner un certain fil de développement pour venir à bout de la problématique posée. Ce qui reviendra à proposer des axes/questions sur les manipulations de cette maquette de TP.

Séance du 05/02/2014 (Rédaction en cours):

Pour bien comprendre les différentes choses à réaliser, on a refait les manipulations vues en TP. On a, pour cela utiliser la maquette didactique TIMS pour générer différent type de modulation:

-la modulation en 4,8,16PSK (on obtient une constellation en forme de cercle).

-La modulation en 4,8,16QAM (on obtient une constellation avec un carré, ou deux: de différentes tailles).

On a très vite dégagé la nécessité de réaliser un montage générateur de tous les mots numériques possibles. On a donc fait un programme sur arduino qui équivaut au générateur pseudo aléatoire. Celui-ci est directement inspiré du montage que l'on a réalisé l'année dernière en conception de circuit électronique. Voir la section "Code Arduino réalisé".

Après on a réfléchi sur la potentielle conception d'une carte FPGA.

Il sera judicieux de ne pas se précipiter sur le schéma et la conception de la carte FPGA, sans avoir, au préalable fait le VHDL et le testez avec un banc de test virtuel.

L'intérêt et de mettre en valeur la nécessité ou non de certains signaux pour le schéma de la carte.

On va mettre en oeuvre les connaissances acquises au S7 en VHDL (en TP de Circuit Numérique Programmble).

Pour ce qui est de l'Arduino, on a répondu aux interrogations suivantes (certaines de ces questions paraissent triviales, mais on préfère éviter les surprises):

Quelle est la vitesse maximale de la communication série de l'Arduino ? -115200bauds

Est-ce que, un programme de type "Analog Write" est-il une vraie sortie analogique ?

-Non, c'est juste une PWM. Elle sera exploitable pour faire les signales I/Q mais très contraignantes, car il faudra filtré le signal, et ce sera beaucoup trop lent (du au fait que la modulation est faite au alentour de 850Mhz), le FPGA sera un passage obligé cela ouvrira les portes d'un plus grand débit.

Code Arduino réalisé:

[code] /*A peut être supprimer*/

- include <avr/io.h>

- include <util/delay.h>

void output_init(void){

DDRB |= 0x02; // PIN 8,9 sont les deux sorties.

}

int main(void){

int r1=1,r2=0,r3=0,r4=0,r5=0,retard=0;

PORTB=0x00;

while(1)

{

r5=r4;//chaque affectation représente une recopie de la bascule sur le "front montant", ici c'est simplement l’exécution du code.

r4=r3;

r3=r2;

r2=r1;

r1=r4^r5;

PORTB=0x01*r1+0x02*retard;//écriture des signaux

_delay_ms(10);//le "front montant", ce qui permet de faire un genre d'horloge.

retard=r5;//déphasage du signal

}

return 0;

} [/code]

Comparaison carte réelle/résultat Arduino:

C'était exactement les signaux attendus (même s'il y un décalage a par rapport à l'original).

On aura bien pour une QPSK (4PSK) tous les couples (ie 00,01,11 et 10).

Séance du 06/02/2014 (Rédaction en cours):

À propos de l'arduino, on pourra envisager une amélioration pour générer une séquence plus longue:

-il faudra simplement utiliser un tableau d'entier.

-paramétrer sa taille avec un N par exemple.

-N correspondra à la taille de séquence de longueur 2^N.

Possibilités de communications:

Exploration des possibilités de communication entre le PC et la carte en amont:

=-> Ethernet:

- + Vitesse de transmission (~10M-100M-G)bauds

- - La gestion du flux de données doit être faite par un microcontrôleur (celui-ci pourra être implémenté un bloc I.P. à l'intérieur du FPGA)

-> - Haute consommation de CLB du FPGA.

-> SPI (communication série):

- - Vitesse de transmission

-> Arduino capable jusqu'a 115200 bauds

-> D'après certaines discussions on pourrait « pousser » au-delà : voir le lien des sujets Raspberry Pi.

-> I2C (recherche à faire):

Communication abandonné, ce n'est pas une priorité.

À propos des blocs I.P.:

En consultant les ordinateurs et en s'appuyant des TPs de CNP, on constate que les blocs suivants existent:

- Xilinx Microblaze/Xilinx Power PC ("µP FPGA")

-> Est-ce possible d'utiliser ces blocs I.P. pour programmer un FPGA sur une carte autre que la Nanoboard ? Comment ?

- EMACx (Ethernet Media Acess Control)(:lien physique entre processeurs et « standart Physical Layer device IEEE802.3)

Conception de la carte:

L'idéal est de se documenter sur la Compatibilité électromagnétique.

2éme semaine: (rédaction en cours) (du 03/02/2014 08/02/2014)

3éme semaine: (rédaction en cours) (du 10/02/2014 15/02/2014)

4éme semaine: (rédaction en cours) (du 17/02/2014 22/02/2014)

5éme semaine: (rédaction en cours) (du 03/03/2014 08/03/2014)

6éme semaine: (rédaction en cours) (du 10/03/2014 15/03/2014)

7éme semaine: (rédaction en cours) (du 17/03/2014 22/03/2014)

Pour les prochaines séances:

Une évaluation du nombre de bits du CAN sera appréciable, il faudrais s'appuyer d'un diagramme des constellations et des tolérances sur l'appertenance des points a un mot.

Pour les manipulations:

On fera la manipulation le 10/02/14 pour tester la chaine composée des composants Minicircuit.

Questions en suspend et idées(Rédaction en cours):

-Comment programmer un FPGA: in situe, ISE Xilinx, matériel requis, programmeur JTAG,

-Communications entre arduinos (en fin de projet) via la chaine

-iInterface USB

Modulateur et démodulateur pour communications numériques

Cahier des charges

Présentation générale du projet

Dans le cadre des TPs d'électronique et de transmission RF, nous avons découvert qu'il existe plusieurs modes de modulation, pour transmettre un signal modulant.

Celles vues en TP au S7 sont la modulation en amplitude, en fréquence, en phase, en BPSK et en QPSK.

Or les modulations en phase, en fréquence et en amplitude étant celles les plus connues, la modulation en QAM (Modulation d'Amplitude en Quadrature) est quant à elle moins connue, mais tout aussi utilisées:

-pour la TNT en 64 QAM (en France).

Fichier:P34 2013 2014 64qam.jpg?

-pour le WiFi en 64-QAM ou 256-QAM (à vérifier).

Or ces deux dernières étant peu représentées au niveau des travaux pratiques, ce projet permettra de fournir un peu plus de pratique sur les modulations de type QAM (en diagramme I/Q) dans le domaine des radiofréquences (~800MHz).

(Le nombre devant le QAM indique le nombre de points dans le diagramme I/Q qu'on appelle aussi constellation)

On se réserve le droit de faire évoluer le cahier des charges a posteriori, si certaines contraintes étaient amenées à évoluer ou se préciser.

Objectif et intérêt du projet

Pour cela, on nous a fourni des modules commerciaux Mini-circuit pouvant travailler dans les radios-fréquences.

Ceux-ci permettront de mettre en place une grande partie de la chaine de transmission (voir schéma de la chaine de transmission).

On a tout d'abord à mettre en place une carte FPGA et/ou un dispositif permettant d'envoyer un flux de données numériques continuellement pour pouvoir visualiser le diagramme I/Q (mise en valeur du diagramme I/Q et voir même un diagramme un peu plus complexe que le BPSK ou le QPSK).

Le canal de transmission qui sera un simple fil électrique, mais pourra devenir une antenne réceptrice et émettrice si le temps imparti le permet (mise en valeur du et mesure du Bit Error Rate qui sera bien sûr différent suivant le canal de transmission).

Du côté réception ,après démodulation du signal, une remise en forme et une interprétation des données seront réalisées, celle-ci dépendra bien entendu de la provenance du flux de données (constater le succès ou l'échec d'un envoi de données).

Enfin si le temps le permets on pourra mettre en une place un système de codage de l'information avec par exemple un codage redondant permettant de corrigé l'erreur (À définir, on pourra faire constater l'efficacité d'une méthode de codage au choix).

Étapes/Déroulement du projet

De même que pour le cahier des charges, il se peut que les étapes diffèrent plus ou moins, en fonction des disponibilités, matérielles et contraintes.

=> Caractérisation des blocs Mini-circuits et épluchage des documentations techniques

Avant de les utiliser dans la chaine de transmission, nous avons à faire une caractérisation des blocs fournis:

-la caractérisation du VCO.

-l'étude des possibilités offerte par le modulateur (cela déterminera le nombre de points possible dans la constellation, ie savoir si l'on peut aller au-delà de la QPSK).

-la caractérisation des mélangeurs (Mixer), leurs facteurs réels de multiplication.

=> Utilisation et exploitation des caractérisations

On pourra ensuite trouver les paramètres pour régler correctement dans notre chaine de transmission certains de nos sous-systèmes comme la boucle à verrouillage de phase.

=> Génération d'un flux des données numériques

Comme dit précédemment, l'idéal et d'avoir un flux de données numériques transmis en permanence. Pour cela plusieurs solutions s'offre à nous, on pourra utiliser un montage générateur pseudo aléatoire (un circuit que l'on a fait l'année dernière en Conception de Circuit Électronique). On pourra "émuler" ce montage avec un Arduino, ou bien même le faire au moyen de la Nanoboard. On pourra aussi transmettre des chaines de caractère en continu.

=> Test de la chaine

Une fois les étapes précédentes réalisées, on pourra passer au test de la chaine de transmission. Il faudra vérifier le bon fonctionnement en aval, dedans (boucle a verrouillage de phase), et en amont de la chaine de transmission.

=> Première mesure du Bit Error Rate

Il sera temps de mesurer/déterminer le B.E.R. de la chaine de transmission avec un fil électrique en tant que canal de transmission. Il est possible que la conception d'un dispositif soit nécessaire que ce soit pour les deux mesures du B.E.R..

=> Antennes

Si toutes les étapes précédentes sont satisfaites, on pourra alors faire un canal de transmission plus intéressant, à savoir l'air. Nous passerons alors à la conception des antennes, émettrice et réceptrice.

=> Deuxième mesure du Bit Error Rate

Il sera temps de mesurer/déterminer le B.E.R. de la chaine de transmission avec un fil électrique en tant que canal de transmission.

=> Codage de l'information et correction d'erreur

En toute fin de ce projet, on pourra même mettre deux dispositifs en aval et en amont de la chaine de transmission. On réalisera alors un codeur et un décodeur permettant de faire de la détection/correction d'erreur.

=> Mise en place d'outil de débogage (tout au long)

La mise en place de simples outils de débogage et primordiale, ceux-ci permettront de vérifier le bon fonctionnement de la chaine.

=> Proposition d'un sujet de TP (tout au long)

Il se trouve que lors du déroulement du projet, on pourra être amené à se poser des questions au niveau des réglages de la chaine de transmission. Or il est fort probable que les élèves qui travailleront sur ce TP pourront alors se poser les mêmes questions. C'est pour cela qui sera judicieux de prendre soin de noter les problématiques rencontrées et de donner un certain fil de développement pour venir à bout de la problématique posée. Ce qui reviendra à proposer des axes/questions sur les manipulations de cette maquette de TP.

Séance du 05/02/2014 (Rédaction en cours):

Pour bien comprendre les différentes choses à réaliser, on a refait les manipulations vues en TP. On a, pour cela utiliser la maquette didactique TIMS pour générer différent type de modulation:

-la modulation en 4,8,16PSK (on obtient une constellation en forme de cercle).

-La modulation en 4,8,16QAM (on obtient une constellation avec un carré, ou deux: de différentes tailles).

On a très vite dégagé la nécessité de réaliser un montage générateur de tous les mots numériques possibles. On a donc fait un programme sur arduino qui équivaut au générateur pseudo aléatoire. Celui-ci est directement inspiré du montage que l'on a réalisé l'année dernière en conception de circuit électronique. Voir la section "Code Arduino réalisé".

Après on a réfléchi sur la potentielle conception d'une carte FPGA.

Il sera judicieux de ne pas se précipiter sur le schéma et la conception de la carte FPGA, sans avoir, au préalable fait le VHDL et le testez avec un banc de test virtuel.

L'intérêt et de mettre en valeur la nécessité ou non de certains signaux pour le schéma de la carte.

On va mettre en oeuvre les connaissances acquises au S7 en VHDL (en TP de Circuit Numérique Programmble).

Pour ce qui est de l'Arduino, on a répondu aux interrogations suivantes (certaines de ces questions paraissent triviales, mais on préfère éviter les surprises):

Quelle est la vitesse maximale de la communication série de l'Arduino ? -115200bauds

Est-ce que, un programme de type "Analog Write" est-il une vraie sortie analogique ?

-Non, c'est juste une PWM. Elle sera exploitable pour faire les signales I/Q mais très contraignantes, car il faudra filtré le signal, et ce sera beaucoup trop lent (du au fait que la modulation est faite au alentour de 850Mhz), le FPGA sera un passage obligé cela ouvrira les portes d'un plus grand débit.

Code Arduino réalisé:

[code] /*A peut être supprimer*/

- include <avr/io.h>

- include <util/delay.h>

void output_init(void){

DDRB |= 0x02; // PIN 8,9 sont les deux sorties.

}

int main(void){

int r1=1,r2=0,r3=0,r4=0,r5=0,retard=0;

PORTB=0x00;

while(1)

{

r5=r4;//chaque affectation représente une recopie de la bascule sur le "front montant", ici c'est simplement l’exécution du code.

r4=r3;

r3=r2;

r2=r1;

r1=r4^r5;

PORTB=0x01*r1+0x02*retard;//écriture des signaux

_delay_ms(10);//le "front montant", ce qui permet de faire un genre d'horloge.

retard=r5;//déphasage du signal

}

return 0;

} [/code]

Comparaison carte réelle/résultat Arduino:

C'était exactement les signaux attendus (même s'il y un décalage a par rapport à l'original).

On aura bien pour une QPSK (4PSK) tous les couples (ie 00,01,11 et 10).

Séance du 06/02/2014 (Rédaction en cours):

À propos de l'arduino, on pourra envisager une amélioration pour générer une séquence plus longue:

-il faudra simplement utiliser un tableau d'entier.

-paramétrer sa taille avec un N par exemple.

-N correspondra à la taille de séquence de longueur 2^N.

Possibilités de communications:

Exploration des possibilités de communication entre le PC et la carte en amont:

=-> Ethernet:

- + Vitesse de transmission (~10M-100M-G)bauds

- - La gestion du flux de données doit être faite par un microcontrôleur (celui-ci pourra être implémenté un bloc I.P. à l'intérieur du FPGA)

-> - Haute consommation de CLB du FPGA.

-> SPI (communication série):

- - Vitesse de transmission

-> Arduino capable jusqu'a 115200 bauds

-> D'après certaines discussions on pourrait « pousser » au-delà : voir le lien des sujets Raspberry Pi.

-> I2C (recherche à faire):

Communication abandonné, ce n'est pas une priorité.

À propos des blocs I.P.:

En consultant les ordinateurs et en s'appuyant des TPs de CNP, on constate que les blocs suivants existent:

- Xilinx Microblaze/Xilinx Power PC ("µP FPGA")

-> Est-ce possible d'utiliser ces blocs I.P. pour programmer un FPGA sur une carte autre que la Nanoboard ? Comment ?

- EMACx (Ethernet Media Acess Control)(:lien physique entre processeurs et « standart Physical Layer device IEEE802.3)

Conception de la carte:

L'idéal est de se documenter sur la Compatibilité électromagnétique.

2éme semaine: (rédaction en cours) (du 03/02/2014 08/02/2014)

3éme semaine: (rédaction en cours) (du 10/02/2014 15/02/2014)

4éme semaine: (rédaction en cours) (du 17/02/2014 22/02/2014)

5éme semaine: (rédaction en cours) (du 03/03/2014 08/03/2014)

6éme semaine: (rédaction en cours) (du 10/03/2014 15/03/2014)

7éme semaine: (rédaction en cours) (du 17/03/2014 22/03/2014)

Pour les prochaines séances:

Une évaluation du nombre de bits du CAN sera appréciable, il faudrais s'appuyer d'un diagramme des constellations et des tolérances sur l'appertenance des points a un mot.

Pour les manipulations:

On fera la manipulation le 10/02/14 pour tester la chaine composée des composants Minicircuit.

Questions en suspend et idées(Rédaction en cours):

-Comment programmer un FPGA: in situe, ISE Xilinx, matériel requis, programmeur JTAG,

-Communications entre arduinos (en fin de projet) via la chaine

-iInterface USB