Communication série, 2013/2014, TD1 : Différence entre versions

| Ligne 110 : | Ligne 110 : | ||

| − | == | + | == Réception == |

(Séance 2 et Séance 3) | (Séance 2 et Séance 3) | ||

Version du 12 juin 2014 à 15:30

Sommaire

Introduction

Ce projet a été réalisé par Ghada Elbez, Sandra Hage, Louis Chauchard et Romain Imbert.

L'objectif de ce projet est de réaliser un circuit électronique qui avait pour mission de gérer le port série présent sur la carte FPGA de la NanoBoard (dans les deux sens c'est à dire émission et réception) ainsi que de réaliser une interface de gestion du port série présent sur la Foxboard.

Gestion du port série de la Nanoboard

Le module RS232 se décompose en deux sous-modules, à savoir une partie émission et une partie réception.

Organisation du projet

Répartition des taches

Progression projet

Partie Informatique

Mise en situation

Transmission

Réception

Implémentation sur la Foxboard

La partie informatique consiste à réaliser une interface Web qui permet de communiquer avec le port série du serveur. Notre site doit être composé d'une seule page HTML qui contient :

- Une zone de texte pour l'émission.

- Une zone de texte pour la réception.

- Un bouton qui permet de commencer.

Les langages utilisés pour notre interface sont : HTML, JavaScript, PHP. Nous avons aussi utiliser des requêtes Ajax pour combiner tous ces langages. Pour cela, nous avons installé la librairie jQuery. Nous avons réalisé d'abord nos test en utilisant un serveur local. Nous avons ensuite copier nos fichiers sur la Foxboard, afin de rendre celle-ci comme un serveur.

Séance 1 (07/05/2014)

Cette séance était consacrée à la compréhension du sujet et à la découverte des différents langages qu'on allait utiliser. Nous avons aussi commencé à faire la page HTML ainsi que quelques fonctions en javascript.

Séance 2 (14/05/2014)

Pendant cette séance nous avons réalisé les deux fichiers PHP d'émission et de réception. Par contre, en testant en utilisant l'Arduino, on recevait bien des informations mais l'émission des données ne fonctionnait pas.

Séance 3 (21/05/2014)

Nous avons corrigé nos erreurs qui se trouvaient dans notre code. Et nous avons configuré notre Foxboard avec le réseau polytech.

Séances supplémentaires

Nous avons copié nos fichiers sur la Foxboard. Et nous avons rédigé le wiki.

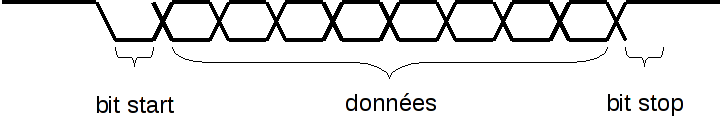

Partie Electronique

Comme on a pu le voir précédemment,la valeur par défaut est à l'état haut. L'envoi du bit de start est représenté par le passage de l'état haut à l'état bas. Ensuite les 8 bits de données sont envoyés à chaque front d'horloge et le dernier (10ème bit) correspond au bit de stop qui permet la remise à la valeur par défaut. De plus, le bit de poids faible est transmis en tête.

Émission

(Séance 1 et Séance 2)

Pour la toute première séance, suite au choix définitif du sujet et de sa compréhension, nous avons effectué plusieurs recherches sur le fonctionnement de la liaison série.

Avant de commencer directement sur le projet, nous avons réalisé le tutoriel d'Altium Designer proposé. Ce qui nous a permis de nous familiariser avec l'utilisation de ce logiciel. En effet, cela nous a permis de comprendre le fonctionnement de la Nanoboard avec les composants des différentes librairies "FPGA".

Ensuite, nous avons commencé réellement le projet, en nous intéressant dans un premier temps à la partie émission, qui nous semblait plus facile. Nous avons rapidement choisi d'utiliser un registre à décalage étant donné que l'on avait eu, au premier semestre, un TP de logique qui permettait de charger des données en parallèles et qui les transmettait ensuite en série.

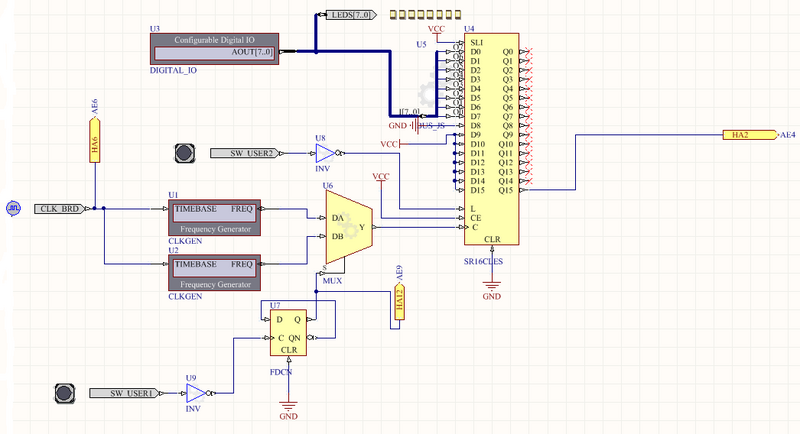

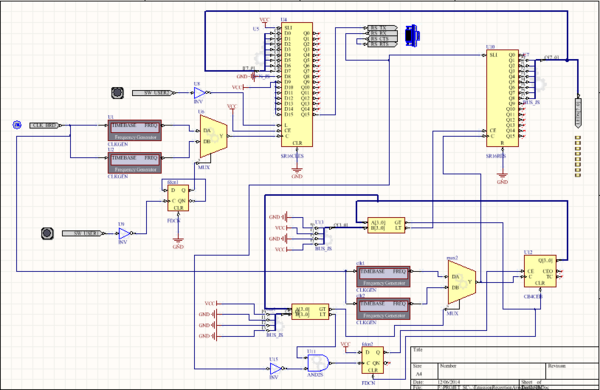

Nous avons donc débuter avec un montage simple qui comporte les éléments suivants:

Un registre à décalage SR16CLES pour convertir Parallèle/Série

Un Configurable Digital IO qui permet de générer les 8 bits de données, reliés au niveau des 8 premières broches du registre à décalage. Les autres sont reliées au VCC. Seul la broche D8 est reliée au GND (masse) pour représenter le bit de start qui est un passage de 1 à 0.

Des LEDs pour visualiser la bonne conversion parallèle/série

Suite à ce test, on a pu constaté que le registre à décalage fonctionne.

Pour la seconde séance, nous avions prévu de continuer et de terminer la partie émission et si possible de commencer la partie réception.

Nous avons gardé le schéma de la première séance, mais nous avons ajouté en plus la possibilité de sélectionner parmi deux vitesses différentes d'émission (sous conseil de nos professeurs). L'utilisation d'un multiplexeur nous a permis de faire cette sélection.

Il suffit de relier deux générateur de fréquence sur les deux entrées du multiplexeur. L'appui sur un bouton de type switch, qui doit être complémenté, sélectionne l'une des deux entrées à générer.

On utilise un bascule D afin de mémoriser le premier appui puis lors du deuxième appui, la valeur mémorisée est complémentée. Ce qui permet d'alterner entre les deux vitesses de transmission possibles, à chaque appui du bouton.

De plus,un second bouton switch est utilisé pour le chargement des données parallèles.

Une fois le schéma réalisé, nous avons effectué des tests en envoyant des trames avec le DIO ainsi que les générateurs d'horloge. Un générateur d'horloge était configuré pour réaliser une vitesse de transmission de 9600 bauds et un autre générateur d'horloge était configuré pour réaliser une vitesse de 4800 bauds.

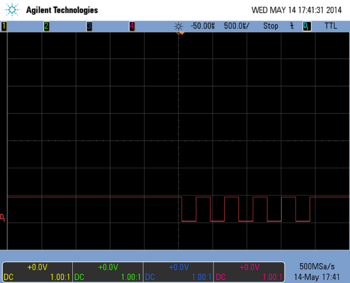

Puis nous avons visualisé avec l'analyseur logique ce que nous obtenions sur une broche du port A de la nanoboard. On remarque bien le bit de start, représenté par le passage de l'état haut à l'état bas.

On remarque que l'on reçoit bien les bits alternés à l'envers, ce qui s'explique par le fait que le bits de poids faible est en-tête. L'émission de bits de données fonctionne donc parfaitement.

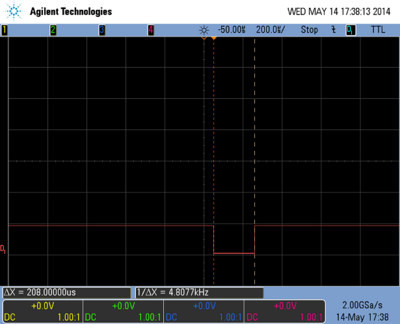

Nous avons de plus, visualiser les fréquences des trames reçues afin de vérifier si nous obtenions bien les deux vitesses de transmissions désirées.

On constate que la structure fonctionne bien.

En effet, dès l'appui du bouton, on passe d'une vitesse de transmission de 9600 bauds (9.6 KHz) à une vitesse de transmission de 4800 bauds (4.8 KHZ).

Réception

(Séance 2 et Séance 3)

La partie émission fonctionnant, nous nous sommes penchés sur la partie Réception du système qui est apparue bien plus complexe.

Suite à l'explication de Monsieur Boé, nous avons compris que pour cette partie, il était nécessaire d'utiliser deux générateur d'horloge de fréquence différente. En effet, si l'on souhaite détecter correctement un bit, il faut se positionner en plein milieu du bit et non pas au niveau d'un front (montant ou descendant) afin d'être sur de détecter un bit et non une perturbation quelconque. Pour se faire, il faut utiliser une deuxième horloge de fréquence deux fois plus rapide pour pouvoir être au milieu du bit.

On reçoit la trame de 10 bits en série à partir de la broche RS RX. Puis le premier front descendant (correspondant au bit de start) doit être détecté pour démarrer le compteur.

La porte AND donnera un 1 logique lorsque ce front sera détecté et que la valeur du compteur sera inférieure ou égale à 1. Ceci va provoquer un front montant au niveau de l’horloge de la bascule D ce qui va permettre le chargement de la valeur de D en sortie (Q).

Cette sortie va donc permettre la mise en route du compteur (broche CE). Ce compteur est donc comparé à la valeur 10 qui valide l’entrée CE du registre U10 pour permettre le décalage.

Si le compteur est strictement supérieur à 10, l’entrée CE du registre U10 (série vers parallèle) devient donc bloquée et ceci va entraîner le blocage du décalage. Au même moment, on remet le compteur à 0 en envoyant un 1 sur son entrée CLR et la sortie Q de la bascule repasse donc à 0 ce qui bloque le compteur U12. Si le compteur est supérieur ou égal à 1, l’entrée de sélection du multiplexeur est égale à 1 ce qui va donc changer la fréquence du compteur.

Malheureusement, cette seconde partie n'a pas donné de résultats concluants, nous n'avons donc pas pu valider son bon fonctionnement.

Assemblage

Conclusion

En conclusion, la partie informatique fonctionne et la partie électronique seule la partie émission fonctionne convenablement, la partie réception ne donne pas de résultats concluants. Ce qui malheureusement, bloque la possibilité de relier les deux parties du projet...