IMA2a4 2022/2023 P1

Sommaire

Présentation générale

Objectifs

Conception, réalisation et programmation d’une clef USB réaliste.

Contexte

En bureau d’études PeiP systèmes embarqués [[1]] nous faisons réaliser des clefs USB aux élèves depuis 3 ans. Mais ces clefs sont très limitées en capacité, les mémoires utilisées, faciles à adresser, ne dépassant pas les quelques Mo. Le but de ce projet est de concevoir une clef USB de l’ordre de quelques Go avec une gestion de mémoire réaliste pour une durée de vie de la clef raisonnable.

Les mémoires flash de grande taille sont :

- généralement à accès parallèle et non série (comme les mémoires SPI utilisées en BE PeiP) ;

- sans aucun mécanisme de gestion de l’usure (comme les mémoires utilisées en BE PeiP) ;

- de type NAND, à savoir que l’on ne peut que transformer des 1 en 0, si l’on souhaite revenir sur des 1, il faut réinitialiser toute une page avec que des 1.

Mais surtout ces mémoires sont imparfaites :

- des erreurs peuvent se produire dans certains blocs (quelques bits mais pas si rarement que cela) ;

- des pages complètes peuvent ne plus pouvoir être réinitialisées (selon les mémoires les pages peuvent être réinitialisées 3000 à 10000 fois suivant les modéles).

Cahier des charges

En plus de la programmation USB de type « mémoire de masse » vous devrez implanter les dispositifs suivants :

- une table pour repérer les pages hors services ;

- un dispositif de correction d’erreur dans les blocs (vous utiliserez l’algorithme de hamming avec un nombre de bits adapté à la fois au taux d’erreurs de la mémoire et à la fois au nombres d’octets disponibles pour stocker ces bits de correction d’erreur) ;

- un dispositif de réduction d’usure comptant le nombre de réinitialisation des pages et permettant de déplacer des blocs souvent modifiés vers d’autres adresses.

Il est fortement recommandé de simuler tous ces dispositifs sur un PC pour tester tous les éléments avant implantation dans le microcontrôleur.

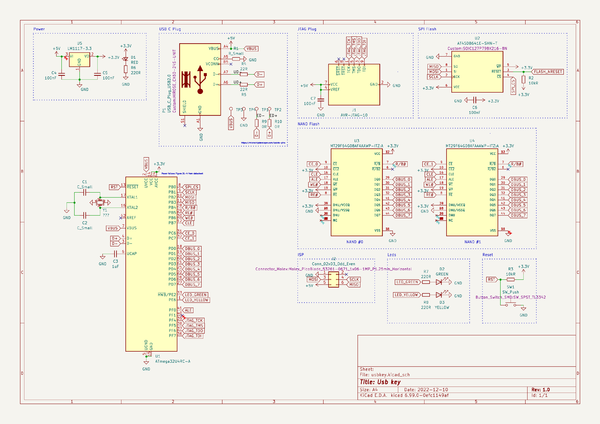

Du coté matériel vous pourrez vous aider des schémas de clefs sur le Wiki des PeiP. Il est cependant conseillé de passer d’un ATMega16u2 à un ATMega32u4 pour disposer de plus d’E/S et de bus. En effet pour implanter les tables nécessaires au fonctionnement des dispositifs décrits ci-dessus, il est conseillé d’ajouter une mémoire SPI plutôt que d’essayer d’implanter les tables sur la mémoire flash principale.

Implantez aussi des points d’accès USB sur votre clef pour pouvoir obtenir des informations sur la gestion des blocs sur la clef :

- lister les pages hors service ;

- récupérer le nombre d’écritures pour des blocs donnés ;

- récupérer le nombre d’erreurs pour des blocs donnés.

Ecrivez aussi le programme PC permettant de récupérer ces informations pour afficher des statistiques sur la clef.

Cahier des spécifications

Diagramme de Gantt prévisionnel

Partie électronique

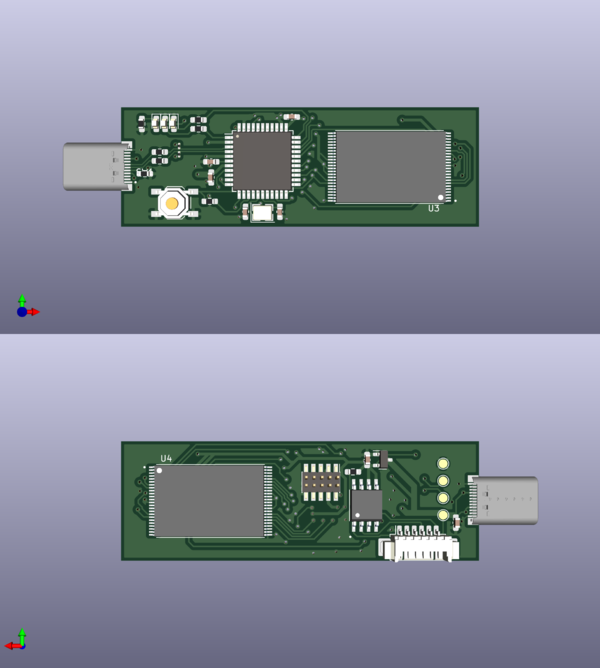

La première version de la clé usb (type C) est équipée d'un Atmega32u4, elle a la capacité d'accueillir deux puces NAND d'une capacité jusqu'à 8Go chacune. La carte expose aussi les points de tests pour utiliser un cable usb 2.0 dans le cas d'un problème avec l'USB type C, trois LEDs (dont une uniquement pour signaler le status alimenté et deux contrôlables directement par le microcontrôleur), un bornier pour l'ISP (ne sera pas soudé par défaut) et d'un bornier pour du JTAG (ne sera pas soudé non plus par défaut). J'aurais aimé aussi inclure une sortie UART pour servir de console durant la phase de développement, cependant tous les pins sont utilisés sauf un.

La carte est quasiment prête pour être envoyée pour fabrication, je fais une dernière passe de vérification durant la semaine et je rajouterais le Gerber et le BOM durant la semaine.

Liens externes

Lien GitLab :

Présentation projet final :

Rapport final :