Reconfiguration d'un FPGA : Différence entre versions

(→Spécifications techniques) |

(→Cahier des charges) |

||

| Ligne 15 : | Ligne 15 : | ||

=== Spécifications techniques === | === Spécifications techniques === | ||

| − | La plateforme choisie pour ce projet est la beaglebone black. C'est un micro-ordinateur miniature embarquant un processeur Texas Instrument, modèle Sitara XAM3359AZCZ100 Cortex A8 ARM cadencé à 1 GHz. | + | La plateforme choisie pour ce projet est la beaglebone black. C'est un micro-ordinateur miniature embarquant un processeur Texas Instrument, modèle Sitara XAM3359AZCZ100 Cortex A8 ARM cadencé à 1 GHz. Une exemplaire de cette plateforme est prêté par Mickaël Coronado pour les besoins du projet. |

[[Fichier:beaglebone.jpg]] | [[Fichier:beaglebone.jpg]] | ||

| Ligne 24 : | Ligne 24 : | ||

L'écriture dans l'EEPROM se fait via interface SPI, qu'il faudra configurer. | L'écriture dans l'EEPROM se fait via interface SPI, qu'il faudra configurer. | ||

| + | |||

| + | === Étapes de la première partie : Ecriture dans l'EEPROM === | ||

| + | |||

| + | * Prise en main de la Beaglebone black (OS, interface de développement, ...) | ||

| + | * Conception d'une carte de test avec une EEPROM et une interface SPI pour tester le programme. La création de la carte est effectué par Inodesign grâce à un schéma qu'il faudra dessiner, à la main ou grâce à un logiciel comme Altium. | ||

| + | * Lire les registres de l'EEPROM : Le début de l'EEPROM est constitué de registres contenant des informations diverses comme sa taille, sa date de fabrication ou son constructeur. Le but est de pouvoir lire ces registres depuis la beaglebone. | ||

| + | * Écrire dans l'EEPROM via SPI | ||

Version du 5 février 2014 à 16:58

Sommaire

Cahier des charges

Suite à la réunion avec Mickaël Coronado, gérant de Inodesign, le cahier des charges suivant a été établi : Alexandre : Ce cahier des charges est beaucoup trop bref.

Contexte

Le but du projet est de permettre une mise à jour aisé d'un FPGA. Il y a deux manières de programmer un FPGA. Soit directement via une liaison J-TAG. Dans ce cas-ci, le FPGA devra être reprogrammé à chaque mise sous tension. Il existe cependant une autre solution, qui consiste à associer une mémoire de type EEPROM au FPGA. Ainsi, il suffit d'écrire le bitstream dans la mémoire, et la mémoire va le charger dans le FPGA à chaque mise sous tension.

L'interface devra aussi pouvoir vérifier l'intégrité des données, afin d'éviter un chargement de bitstream corrompu.

L'autre partie du projet consiste à gérer la partie récupération du bitstream par FTP, ou mieux par SFTP. L'ensemble devra donc être autonome, de la récupération du bitstream à programmation du FPGA.

Spécifications techniques

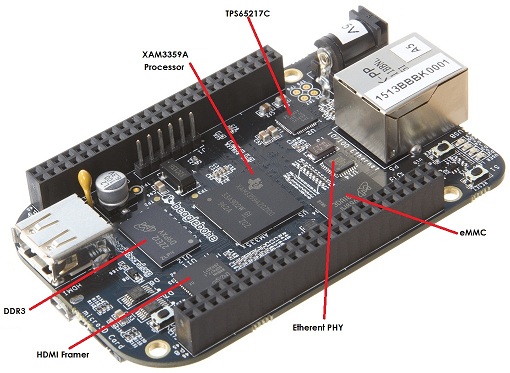

La plateforme choisie pour ce projet est la beaglebone black. C'est un micro-ordinateur miniature embarquant un processeur Texas Instrument, modèle Sitara XAM3359AZCZ100 Cortex A8 ARM cadencé à 1 GHz. Une exemplaire de cette plateforme est prêté par Mickaël Coronado pour les besoins du projet.

Un système d'exploitation est inclus de base dans la eMMC de la beaglebone. Il faudra savoir si cela suffit pour développer le programme, ou s'il faut installer un autre OS.

Le langage choisi est le C.

L'écriture dans l'EEPROM se fait via interface SPI, qu'il faudra configurer.

Étapes de la première partie : Ecriture dans l'EEPROM

- Prise en main de la Beaglebone black (OS, interface de développement, ...)

- Conception d'une carte de test avec une EEPROM et une interface SPI pour tester le programme. La création de la carte est effectué par Inodesign grâce à un schéma qu'il faudra dessiner, à la main ou grâce à un logiciel comme Altium.

- Lire les registres de l'EEPROM : Le début de l'EEPROM est constitué de registres contenant des informations diverses comme sa taille, sa date de fabrication ou son constructeur. Le but est de pouvoir lire ces registres depuis la beaglebone.

- Écrire dans l'EEPROM via SPI