Reconfiguration d'un FPGA : Différence entre versions

(→Cahier des charges) |

(→Cahier des charges) |

||

| Ligne 7 : | Ligne 7 : | ||

=== Contexte === | === Contexte === | ||

| − | Le but du projet est de permettre une mise à jour aisé d'un FPGA. Il y a deux manières de programmer un FPGA. Soit directement via une liaison J-TAG. Dans ce cas-ci, le FPGA devra être reprogrammé à chaque mise sous tension. Il existe cependant une autre solution, qui consiste à associer une mémoire de type EEPROM au FPGA. Ainsi, il suffit d'écrire le | + | Le but du projet est de permettre une mise à jour aisé d'un FPGA. Il y a deux manières de programmer un FPGA. Soit directement via une liaison J-TAG. Dans ce cas-ci, le FPGA devra être reprogrammé à chaque mise sous tension. Il existe cependant une autre solution, qui consiste à associer une mémoire de type EEPROM au FPGA. Ainsi, il suffit d'écrire le bitstream dans la mémoire, et la mémoire va le charger dans le FPGA à chaque mise sous tension. |

| − | === | + | L'interface devra aussi pouvoir vérifier l'intégrité des données, afin d'éviter un chargement de bitstream corrompu. |

| + | |||

| + | L'autre partie du projet consiste à gérer la partie récupération du bitstream par FTP, ou mieux par SFTP. L'ensemble devra donc être autonome, de la récupération du bitstream à programmation du FPGA. | ||

| + | |||

| + | === Spécifications techniques === | ||

| + | |||

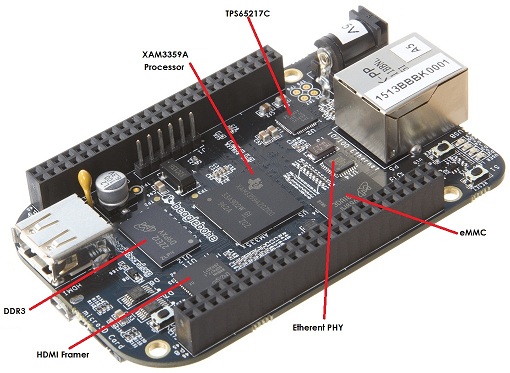

| + | La plateforme choisie pour ce projet est la beaglebone black. C'est un micro-ordinateur miniature embarquant un processeur Texas Instrument, modèle Sitara XAM3359AZCZ100 Cortex A8 ARM cadencé à 1 GHz | ||

| + | |||

| + | [[Fichier:beaglebone.jpg]] | ||

Version du 5 février 2014 à 16:32

Cahier des charges

Suite à la réunion avec Mickaël Coronado, gérant de Inodesign, le cahier des charges suivant a été établi : Alexandre : Ce cahier des charges est beaucoup trop bref.

Contexte

Le but du projet est de permettre une mise à jour aisé d'un FPGA. Il y a deux manières de programmer un FPGA. Soit directement via une liaison J-TAG. Dans ce cas-ci, le FPGA devra être reprogrammé à chaque mise sous tension. Il existe cependant une autre solution, qui consiste à associer une mémoire de type EEPROM au FPGA. Ainsi, il suffit d'écrire le bitstream dans la mémoire, et la mémoire va le charger dans le FPGA à chaque mise sous tension.

L'interface devra aussi pouvoir vérifier l'intégrité des données, afin d'éviter un chargement de bitstream corrompu.

L'autre partie du projet consiste à gérer la partie récupération du bitstream par FTP, ou mieux par SFTP. L'ensemble devra donc être autonome, de la récupération du bitstream à programmation du FPGA.

Spécifications techniques

La plateforme choisie pour ce projet est la beaglebone black. C'est un micro-ordinateur miniature embarquant un processeur Texas Instrument, modèle Sitara XAM3359AZCZ100 Cortex A8 ARM cadencé à 1 GHz