IMA5 2021/2022 P29 : Différence entre versions

(→) |

(→) |

||

| (4 révisions intermédiaires par le même utilisateur non affichées) | |||

| Ligne 109 : | Ligne 109 : | ||

[[Fichier:PI_DELABRE_NRF52840.jpg]] | [[Fichier:PI_DELABRE_NRF52840.jpg]] | ||

| + | [1] | ||

| Ligne 135 : | Ligne 136 : | ||

[[Fichier:PI_DELABRE_B3A7.jpg]] | [[Fichier:PI_DELABRE_B3A7.jpg]] | ||

| + | [2] | ||

== == | == == | ||

| − | Rédaction code VHDL permettant d'envoyer un signal de clock générant un glitch | + | *Rédaction code VHDL permettant d'envoyer un signal de clock générant un glitch |

== == | == == | ||

| Ligne 146 : | Ligne 148 : | ||

== == | == == | ||

| + | [1] https://fr.farnell.com/ | ||

| + | |||

| + | [2] https://www.lextronic.fr/ | ||

== == | == == | ||

=Documents Rendus= | =Documents Rendus= | ||

Version actuelle datée du 14 janvier 2022 à 12:30

Présentation générale

Description

De nos jours, les objets connectés font partie de notre quotidien avec des prix de moins en moins élevés, ces objets sont souvent connectés en bluetooth. Ce projet a pour but de mettre en place un protocole d’attaque permettant de récupérer le programme sur des objets connectés de la vie de tous les jours.

Objectifs

L’objectif de ce projet est, dans un premier temps, de comprendre et de tester des attaques en perturbant le comportement du microcontrôleur afin de récupérer ses données. Puis, dans un second temps, de mettre en place un protocole détaillant les différentes étapes d’une attaque ainsi que les méthodes utilisées afin de pouvoir la reproduire sur divers objets connectés.

Préparation du projet

Cahier des charges

Choix techniques

Attaques

Attaques en fautes non invasives :

- perturbation de l’horloge

- perturbation de la tension d’alimentation

Matériel :

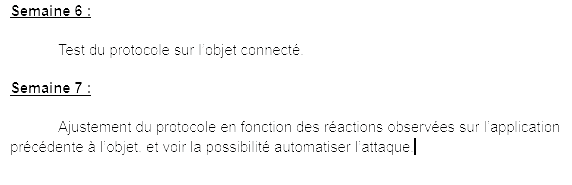

nRF52 et son IDE

Accès au salle de TP afin d'avoir accès à une nanoboard, des ordinateurs avec Altium et une alimentation

Liste des tâches à effectuer

- Bibliographie

- Choix et commande du matériel

- Ecriture d'un programme sur le microcontrôleur

- Réalisation du banc de test

- Test des différentes attaques

- Mise en place d'un protocole d'attaque

- Test du protocole d'attaque sur un objet connecté

Calendrier prévisionnel

semaine 1

Commande du matériel et écriture du programme sur le nRF52

Documentation sur les attaques en fautes non invasives et la récupération des données

Lecture de la datasheet du microcontrôleur

Bibliographie à remplir

semaine 2

Mise en place du banc de test :

écriture programme en vhdl pour changer la clock

semaine 3

Premiers tests d'attaques avec perturbation de l'horloge

semaine 4

Premiers tests d'attaques avec perturbation de la tension

semaine 5

Mise en place du protocole

Choix et commande de l'objet connecté ( si possible)

semaine 6

Test du protocole sur un objet connecté

Réalisation du projet

- Réalisation du cahier des charges

- Lecture de document/Visionnage de vidéo afin d'en savoir plus sur la nRF52.

- Rédaction du cahier des spécifications :

- Lecture de document, ajout à la bibliographie.

- Choix du nRF52xxx à acheter, et demande à l'école pour la commande :

- Rédaction du premier code à tester sur la nRF52, exemple de code fourni sur NordicSemiconductor ainsi que les librairies et drivers nécessaire :

https://www.nordicsemi.com/Products/Development-software/nRF5-SDK

- Recherches bibliographiques

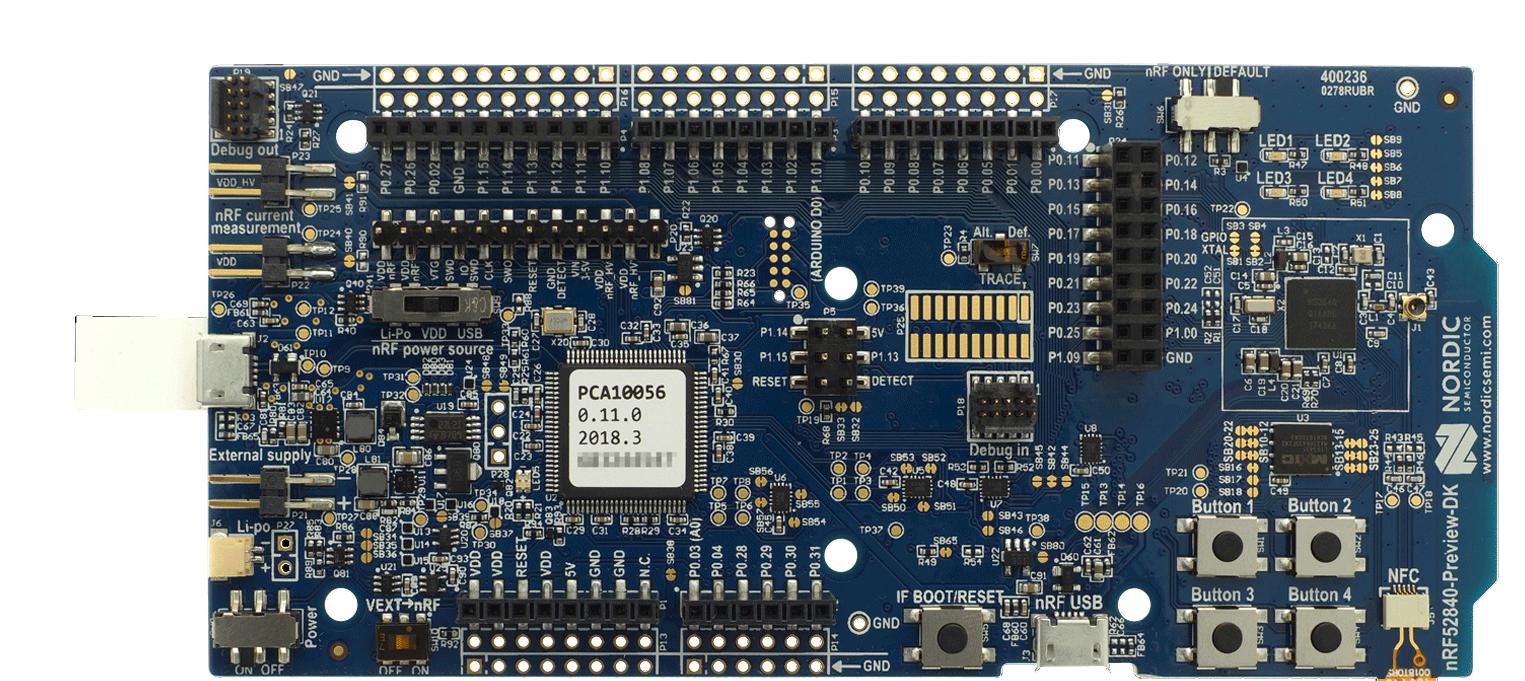

- Installation logiciel pour piloter carte nRF52840, ce dernier permet de téléverser le code sur la NRF52840 ( le code doit être en format ".hex" ), il permet aussi un suivi de l'alimentation de la carte lorsqu'elle est connecté à l'ordinateur ainsi qu'un suivi de la puissance de réception Bluetooth :

https://www.nordicsemi.com/Products/Development-software/nRF-Connect-SDK

Pour obtenir le code en C en .hex j'ai utilisé "Keil µVision5"

- Mise en pratique de la théorie vu sur les différents documents, l'attaque Clock glitch doit être réalisé en injectant un glitch dans le signal d'horloge de la NRF52840, j'ai donc pensé à utiliser un fpga qui me permettrait de générer un signal d'horloge comme je le souhaite.

- Installation Vivado sur mon ordinateur perso ( problème de détection du FPGA sur les PC de l'école ).

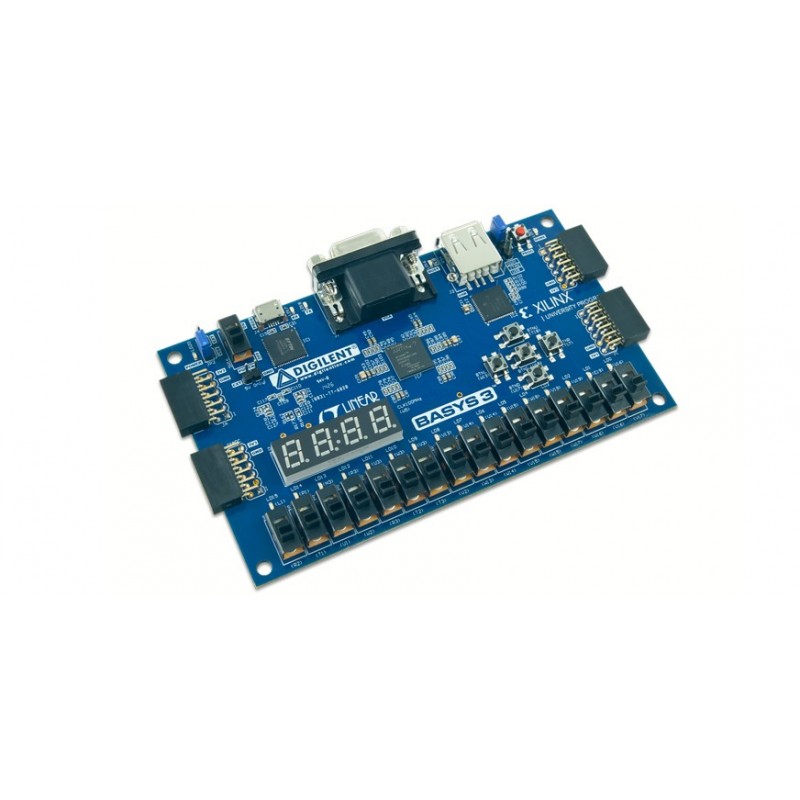

- Le FPGA que l'école me permet d'utiliser est le Basys 3 Artix-7 :

- Rédaction code VHDL permettant d'envoyer un signal de clock générant un glitch

- A la réception de la commande des NRF52840 il était nécessaire d'installer le firmware

- Test du code commencé plus tôt, modification jusqu'à obtenir quelque chose de fonctionnelle