| MODEL NO :     | ET024QV01-K      |  |

|----------------|------------------|--|

| MODEL VERSION: | 01               |  |

| SPEC VERSION:  | 1.0              |  |

| ISSUED DATE:   | 2017-12-05       |  |

| ■Prelimina     | ry Specification |  |

|                | luct Specificati |  |

Customer :\_\_\_\_

| Approved by | Notes |

|-------------|-------|

|             |       |

|             |       |

|             |       |

|             |       |

# **Table of Contents**

| Re | cord of Revision                   | 3 |

|----|------------------------------------|---|

| 1  | General Specifications             | 4 |

|    | Input/Output Terminals             |   |

|    | Absolute Maximum Ratings           |   |

|    | Electrical Characteristics         |   |

|    | Timing Chart                       |   |

|    | Optical Characteristics            | - |

|    | Environmental / Reliability Test   |   |

|    | Packing Drawing                    |   |

|    | Precautions for Use of LCD Modules |   |

# **Record of Revision**

| Rev | Issued Date | Description                       | Editor      |

|-----|-------------|-----------------------------------|-------------|

| 1.0 | 2017-12-05  | Preliminary Specification Release | Xunqiang Ji |

|     |             |                                   |             |

|     |             |                                   | ///         |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

|     |             |                                   |             |

| 1   |             |                                   |             |

| 1   |             |                                   |             |

|     |             |                                   |             |

# 1 General Specifications

|                 | Feature              | Spec                           |

|-----------------|----------------------|--------------------------------|

|                 | Size                 | 2.4 inch                       |

|                 | Resolution           | 240 x RGB x 320                |

|                 | Technology Type      | a-Si                           |

| Display Spec.   | Pixel Configuration  | RGB Vertical Stripe            |

|                 | Pixel pitch(mm)      | 0.153 x 0.153                  |

|                 | Display Mode         | Transf lective /Normally Black |

|                 | Viewing Direction    | ALL                            |

|                 | LCM (W x H x D) (mm) | 42.92X60.26X2.45               |

| Mechanical      | Active Area(mm)      | 36.72(H) *48.96(V)             |

| Characteristics | With /Without TSP    | Without TSP                    |

|                 | LED Numbers          | 4 LEDS                         |

|                 | Driver IC            | ST7789V                        |

|                 | Weight (g)           | TBD                            |

| Electrical      | Interface            | RGB/MCU Interface              |

| Characteristics | Color Depth          | 262K                           |

Note 1: Viewing direction for best image quality is different from TFT definition. There is a 180 degree shift.

Note 2: Requirements on Environmental Protection: Q/S0002

Note 3: LCM weight tolerance: ± 5%

# 2 Input/Output Terminals

| NO.   | SYMBOL      | DISCRIPTION                                                                                                                                                                                                                                                     | I/O |

|-------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1     | GND         | Ground.                                                                                                                                                                                                                                                         | Р   |

| 2     | VCI         | Supply voltage(3.3V).                                                                                                                                                                                                                                           | Р   |

| 3     | IOVCC       | Supply voltage(1.65-3.3V).                                                                                                                                                                                                                                      | Р   |

| 4     | IM2         | MPU Parallel interface bus and serial interface select If use RGB                                                                                                                                                                                               | I   |

| 5     | IM1         | Interface must select serial interface.                                                                                                                                                                                                                         | I   |

| 6     | IM0         | Fix this pin at VCI and GND.                                                                                                                                                                                                                                    | ı   |

| 7     | RESET       | This signal will reset the device and must be applied to properly initialize the chip.                                                                                                                                                                          | ı   |

| 8     | CS          | Chip select input pin ("Low" enable). fix this pin at VCI or GND when not in use.                                                                                                                                                                               | I   |

| 9     | DC(SPI-SCL) | -Display data/command selection pin in parallel interfaceThis pin is used to be serial interface clock. DC='1': display data or parameter. DC='0': command dataIf not used, please fix this pin at VDDI or DGND.                                                | I   |

| 10    | WR(SPI-RS)  | <ul> <li>-Write enable in MCU parallel interface.</li> <li>- Display data/command selection pin in 4-line serial interface.</li> <li>- Second Data lane in 2 data lane serial interface.</li> <li>-If not used, please fix this pin at VDDI or DGND.</li> </ul> | I   |

| 11    | RD          | Serves as a read signal and MCU read data at the rising edge. fix this pin at VCI or GND when not in use.                                                                                                                                                       | I   |

| 12    | VSYNC       | Frame synchronizing signal for RGB interface operation. fix this pin at VCI or GND when not in use.                                                                                                                                                             | I   |

| 13    | HSYNC       | Line synchronizing signal for RGB interface operation. fix this pin at VCI or GND when not in use.                                                                                                                                                              | I   |

| 14    | ENABLE      | Data enable signal for RGB interface operation. fix this pin at VCI or GND when not in use.                                                                                                                                                                     | I   |

| 15    | DOTCLK      | Dot clock signal for RGB interface operation.  Fix this pin at VCI or GND when not in use.                                                                                                                                                                      | 1   |

| 16    | SDA         | Serial input signal.  The data is latched on the rising edge of the SCL signal.  fix this pin at VCI or GND when not in use.                                                                                                                                    | I   |

| 17-34 | DB0-DB17    | 18-bit parallel bi-directional data bus for MCU system and RGB i                                                                                                                                                                                                | 1/0 |

|    |        | nterface mode .                                                                                                         |     |

|----|--------|-------------------------------------------------------------------------------------------------------------------------|-----|

|    |        | Fix to GND level when not in use                                                                                        |     |

| 35 | SDO    | SPI interface output pin.  -The data is output on the falling edge of the SCL signal.  -If not used, let this pin open. | 0   |

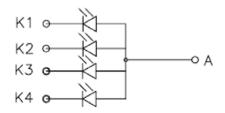

| 36 | LEDA   | Anode pin of backlight                                                                                                  | Р   |

| 37 | LEDK1  | Cathode pin OF backlight                                                                                                | Р   |

| 38 | LEDK2  | Cathode pin OF backlight                                                                                                | Р   |

| 39 | LEDK3  | Cathode pin OF backlight                                                                                                | Р   |

| 40 | LEDK4  | Cathode pin OF backlight                                                                                                | Р   |

| 41 | XR(NC) | Touch panel Right Glass Terminal                                                                                        | A/D |

| 42 | YU(NC) | Touch panel Bottom Film Terminal                                                                                        | A/D |

| 43 | XL(NC) | Touch panel LIFT Glass Terminal                                                                                         | A/D |

| 44 | YD(NC) | Touch panel Top Film Terminal                                                                                           | A/D |

| 45 | GND    | Ground.                                                                                                                 | Р   |

# 3 Absolute Maximum Ratings

| Characteristics                  | Symbol          | Min. | Max. | Unit       |

|----------------------------------|-----------------|------|------|------------|

| Digital Supply Voltage           | VCI             | -0.3 | 4.6  | V          |

| Digital Interface Supply Voltage | IOVCC           | -0.3 | 4.6  |            |

| Operating temperature            | T <sub>OP</sub> | -20  | +70  | $^{\circ}$ |

| Storage temperature              | T <sub>ST</sub> | -30  | +80  | $^{\circ}$ |

## 4 Electrical Characteristics

## 4.1 Driving TFT LCD Panel

| Characteristics                  | Symbol          | Min.     | Тур. | Max.     | Unit | Note |

|----------------------------------|-----------------|----------|------|----------|------|------|

| Digital Supply Voltage           | VCI             | 2.4      | 2.75 | 3.3      | ٧    |      |

| Digital Interface Supply Voltage | IOVCC           | 1.65     | 1.8  | 3.3      |      |      |

| Normal mode Current consumption  | IDD             | -        | 8    | -        | mA   |      |

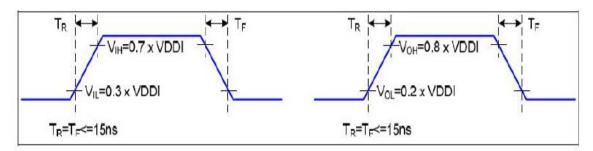

| l aval involvedta as             | V <sub>IH</sub> | 0.7VDDIO |      | VDDIO    | ٧    |      |

| Level input voltage              | VIL             | GND      |      | 0.3VDDIO | ٧    |      |

| Laval autout valtage             | V <sub>OH</sub> | 0.8VDDIO |      | VDDIO    | ٧    |      |

| Level output voltage             | VoL             | GND      |      | 0.2VDDIO | ٧    |      |

## 4.2 Backlight Unit

The backlight system is an edge-lighting type with 4 LED. The characteristics of the LED are shown in the following tables.

| Item            | Symbol  | MIN   | TYP | MAX | Unit | Remark |

|-----------------|---------|-------|-----|-----|------|--------|

| Backlight       |         |       | 0.0 |     |      |        |

| forward voltage | $V_{F}$ | -     | 3.2 | -   | V    |        |

| Backlight       |         |       |     |     |      | 4 LEDs |

| forward current | lF      | -     | 80  | -   | mA   |        |

| LED life time   | -       | 50000 | -   | 1   | Hrs  |        |

Note 1: LED life time (Hr) can be defined as the time in which it continues to operate under the condition: Ta=25 $\pm$ 3  $^{\circ}$ C, typical IL value indicated in the above table and the fL=50k Hz until the brightness becomes less than 50%.

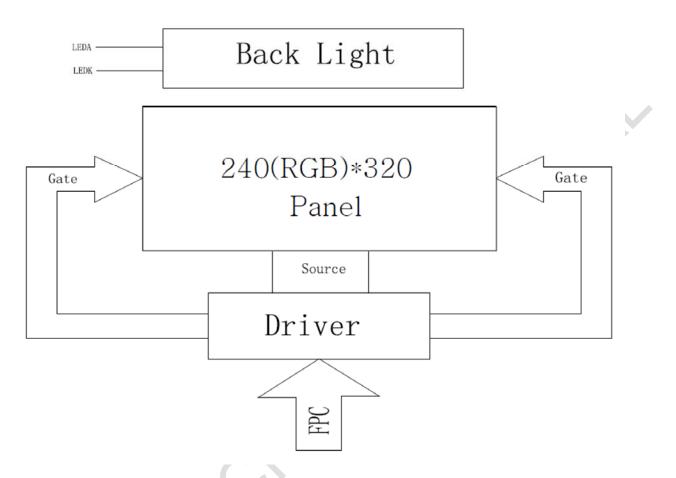

# 4.3 Block Diagram LCD Module diagram

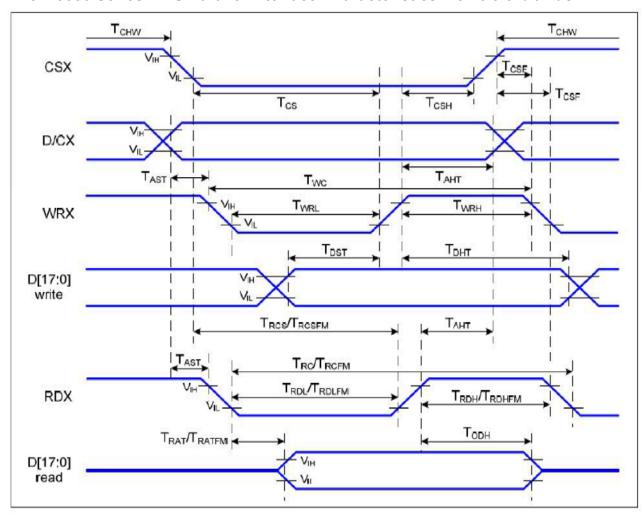

## 5 Timing Chart

## 5.1 8080 Series MCU Parallel Interface Characteristics: 18/16/9/8-bit Bus

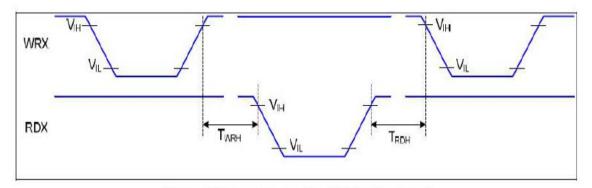

Figure 1 Parallel Interface Timing Characteristics (8080-Series MCU Interface)

VDDI=1.65 to 3.3V, VDD=2.4 to 3.3V, AGND=DGND=0V, Ta=25℃

| Signal   | Symbol             | Parameter                          | Min | Max | Unit | Description       |

|----------|--------------------|------------------------------------|-----|-----|------|-------------------|

| DIOV     | T <sub>AST</sub>   | Address setup time                 | 0   |     | ns   |                   |

| D/CX     | T <sub>AHT</sub>   | Address hold time (Write/Read)     | 10  |     | ns   | -                 |

|          | T <sub>CHW</sub>   | Chip select "H" pulse width        | 0   |     | ns   |                   |

|          | T <sub>cs</sub>    | Chip select setup time (Write)     | 15  |     | ns   |                   |

| CSX      | T <sub>RCS</sub>   | Chip select setup time (Read ID)   | 45  |     | ns   |                   |

| CSX      | T <sub>RCSFM</sub> | Chip select setup time (Read FM)   | 355 |     | ns   | -                 |

| ř        | T <sub>CSF</sub>   | Chip select wait time (Write/Read) | 10  |     | ns   |                   |

| 5        | T <sub>CSH</sub>   | Chip select hold time              | 10  |     | ns   |                   |

|          | T <sub>wc</sub>    | Write cycle                        | 66  |     | ns   |                   |

| WRX      | T <sub>WRH</sub>   | Control pulse "H" duration         | 15  |     | ns   |                   |

| 8        | T <sub>WRL</sub>   | Control pulse "L" duration         | 15  |     | ns   |                   |

| **       | T <sub>RC</sub>    | Read cycle (ID)                    | 160 |     | ns   |                   |

| RDX (ID) | T <sub>RDH</sub>   | Control pulse "H" duration (ID)    | 90  |     | ns   | When read ID data |

|          | T <sub>RDL</sub>   | Control pulse "L" duration (ID)    | 45  |     | ns   |                   |

| DDV      | T <sub>RCFM</sub>  | Read cycle (FM)                    | 450 |     | ns   | 16/1              |

| RDX      | T <sub>RDHFM</sub> | Control pulse "H" duration (FM)    | 90  |     | ns   | When read from    |

| (FM)     | T <sub>RDLFM</sub> | Control pulse "L" duration (FM)    | 355 |     | ns   | frame memory      |

| D[17:0]  | T <sub>DST</sub>   | Data setup time                    | 10  |     | ns   | For CL=30pF       |

Version 1.4 Page 41 of 316 2014/10

Sitronix Confidential The information contained herein is the exclusive property of Sitronix and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Sitronix.

| T <sub>DHT</sub>   | Data hold time        | 10 |     | ns |

|--------------------|-----------------------|----|-----|----|

| T <sub>RAT</sub>   | Read access time (ID) | 7  | 40  | ns |

| T <sub>RATEM</sub> | Read access time (FM) |    | 340 | ns |

| T <sub>ODH</sub>   | Output disable time   | 20 | 80  | ns |

Table 4 8080 Parallel Interface Characteristics

Figure 2 Rising and Falling Timing for I/O Signal

Figure 3 Write-to-Read and Read-to-Write Timing

Note: The rising time and falling time (Tr, Tf) of input signal and fall time are specified at 15 ns or less. Logic high and low levels are specified as 30% and 70% of VDDI for Input signals.

## 5.2 Serial Interface Characteristics (3-line serial)

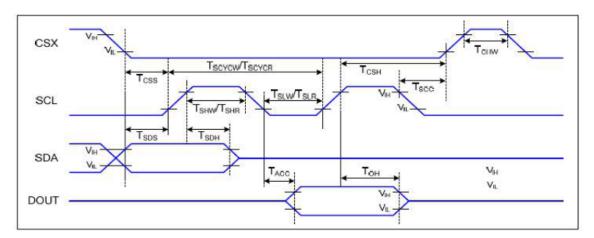

Figure 4 3-line serial Interface Timing Characteristics

VDDI=1.65 to 3.3V, VDD=2.4 to 3.3V, AGND=DGND=0V, Ta=25 C

| Signal | Symbol             | Parameter                      | Min | Max | Unit | Description         |

|--------|--------------------|--------------------------------|-----|-----|------|---------------------|

|        | T <sub>CSS</sub>   | Chip select setup time (write) | 15  |     | ns   |                     |

|        | T <sub>CSH</sub>   | Chip select hold time (write)  | 15  |     | ns   |                     |

| CSX    | T <sub>CSS</sub>   | Chip select setup time (read)  | 60  |     | ns   |                     |

|        | T <sub>scc</sub>   | Chip select hold time (read)   | 65  |     | ns   |                     |

|        | T <sub>CHW</sub>   | Chip select "H" pulse width    | 40  |     | ns   |                     |

|        | T <sub>scycw</sub> | Serial clock cycle (Write)     | 66  |     | ns   |                     |

|        | T <sub>SHW</sub>   | SCL "H" pulse width (Write)    | 15  |     | ns   |                     |

| CCI    | T <sub>SLW</sub>   | SCL "L" pulse width (Write)    | 15  |     | ns   |                     |

| SCL    | T <sub>SCYCR</sub> | Serial clock cycle (Read)      | 150 |     | ns   |                     |

|        | T <sub>SHR</sub>   | SCL "H" pulse width (Read)     | 60  |     | ns   |                     |

|        | T <sub>SLR</sub>   | SCL "L" pulse width (Read)     | 60  |     | ns   |                     |

| SDA    | T <sub>SDS</sub>   | Data setup time                | 10  |     | ns   |                     |

| (DIN)  | T <sub>SDH</sub>   | Data hold time                 | 10  |     | ns   |                     |

| DOUT   | T <sub>ACC</sub>   | Access time                    | 10  | 50  | ns   | For maximum CL=30pF |

| DOUT   | Тон                | Output disable time            | 15  | 50  | ns   | For minimum CL=8pF  |

Table 5 3-line serial Interface Characteristics

Note: The rising time and falling time (Tr, Tf) of input signal are specified at 15 ns or less. Logic high and low levels are specified as

30% and 70% of VDDI for Input signals.

## 5.3 Serial Interface Characteristics (4-line serial)

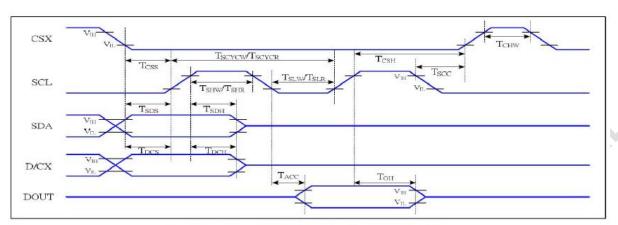

Figure 5 4-line serial Interface Timing Characteristics

VDDI=1.65 to 3.3V, VDD=2.4 to 3.3V, AGND=DGND=0V, Ta=25℃

| Signal | Symbol             | Parameter                      | MIN | MAX | Unit | Description           |

|--------|--------------------|--------------------------------|-----|-----|------|-----------------------|

|        | T <sub>CSS</sub>   | Chip select setup time (write) | 15  |     | ns   |                       |

|        | T <sub>CSH</sub>   | Chip select hold time (write)  | 15  |     | ns   |                       |

| CSX    | T <sub>CSS</sub>   | Chip select setup time (read)  | 60  |     | ns   |                       |

|        | T <sub>scc</sub>   | Chip select hold time (read)   | 65  |     | ns   |                       |

|        | T <sub>CHW</sub>   | Chip select "H" pulse width    | 40  |     | ns   |                       |

| SCL    | T <sub>SCYCW</sub> | Serial clock cycle (Write)     | 66  |     | ns   | 10.11                 |

|        | T <sub>SHW</sub>   | SCL "H" pulse width (Write)    | 15  |     | ns   | -write command & data |

|        | T <sub>SLW</sub>   | SCL "L" pulse width (Write)    | 15  | 10  | ns   | ram                   |

|        | T <sub>SCYCR</sub> | Serial clock cycle (Read)      | 150 |     | ns   |                       |

|        | T <sub>SHR</sub>   | SCL "H" pulse width (Read)     | 60  |     | ns   | -read command & data  |

|        | T <sub>SLR</sub>   | SCL "L" pulse width (Read)     | 60  |     | ns   | ram                   |

| D/OV   | T <sub>DCS</sub>   | D/CX setup time                | 10  |     | ns   |                       |

| D/CX   | Тосн               | D/CX hold time                 | 10  |     | ns   |                       |

| SDA    | T <sub>SDS</sub>   | Data setup time                | 10  |     | ns   |                       |

| (DIN)  | T <sub>SDH</sub>   | Data hold time                 | 10  |     | ns   |                       |

| DOUT   | TACC               | Access time                    | 10  | 50  | ns   | For maximum CL=30pF   |

| DOUT   | T <sub>OH</sub>    | Output disable time            | 15  | 50  | ns   | For minimum CL=8pF    |

Table 6 4-line serial Interface Characteristics

Note: The rising time and falling time (Tr, Tf) of input signal are specified at 15 ns or less. Logic high and low levels are specified as

Version 1.4 Page 44 of 316 2014/10

Sitronix Confidential The information contained herein is the exclusive property of Sitronix and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Sitronix.

## 5.4 RGB Interface Characteristics

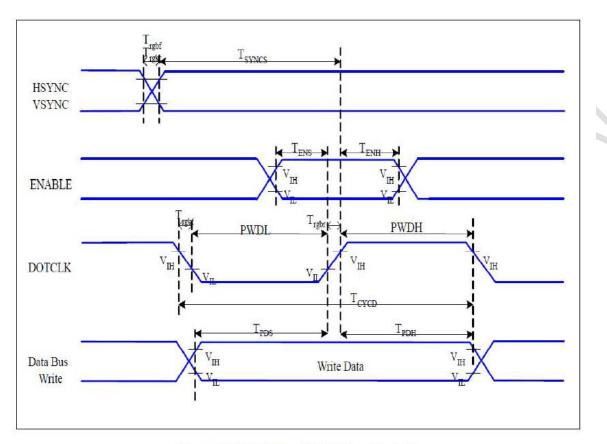

Figure 6 RGB Interface Timing Characteristics

VDDI=1.65 to 3.3V, VDD=2.4 to 3.3V, AGND=DGND=0V, Ta=25℃

| Signal          | Symbol            | Parameter                     | MIN                        | MAX | Unit | Description |

|-----------------|-------------------|-------------------------------|----------------------------|-----|------|-------------|

| HSYNC,<br>VSYNC | Tsyncs            | VSYNC, HSYNC Setup Time       | VSYNC, HSYNC Setup Time 30 |     |      |             |

| ENABLE          | T <sub>ENS</sub>  | Enable Setup Time             | 25                         |     | ns   |             |

| ENABLE          | T <sub>ENH</sub>  | Enable Hold Time              | 25                         |     | ns   |             |

|                 | PWDH              | DOTCLK High-level Pulse Width | 60                         | -   | ns   |             |

| DOTCLK          | PWDL              | DOTCLK Low-level Pulse Width  | 60                         | -   | ns   |             |

| DOTCER          | T <sub>CYCD</sub> | DOTCLK Cycle Time             | 120                        |     | ns   |             |

|                 | Trghr, Trghf      | DOTCLK Rise/Fall time         | -                          | 20  | ns   |             |

| - DD            | T <sub>PDS</sub>  | PD Data Setup Time            | 50                         |     | ns   |             |

| DB              | T <sub>PDH</sub>  | PD Data Hold Time             | 50                         |     | ns   |             |

Table 7 18/16 Bits RGB Interface Timing Characteristics

## Model No.ET024QV01

| Signal          | Symbol             | Parameter               | MIN | MAX | Unit | Description |

|-----------------|--------------------|-------------------------|-----|-----|------|-------------|

| HSYNC,<br>VSYNC | T <sub>SYNCS</sub> | VSYNC, HSYNC Setup Time | 25  | -   | ns   |             |

| ENABLE          | T <sub>ENS</sub>   | Enable Setup Time       | 25  | -   | ns   |             |

Version 1.4 Page 46 of 316 2014/10

Sitronix Confidential The information contained herein is the exclusive property of Sitronix and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Sitronix.

|        | T <sub>ENH</sub> | Enable Hold Time              | 25 | -              | ns |  |

|--------|------------------|-------------------------------|----|----------------|----|--|

|        | PWDH             | DOTCLK High-level Pulse Width | 25 | t <del>e</del> | ns |  |

| DOTOLK | PWDL             | DOTCLK Low-level Pulse Width  | 25 | -              | ns |  |

| DOTCLK | Tcycb            | DOTCLK Cycle Time             | 55 | (T.)           | ns |  |

|        | Trghr, Trghf     | DOTCLK Rise/Fall time         | -  | 10             | ns |  |

| 20     | T <sub>PDS</sub> | PD Data Setup Time            | 25 | -              | ns |  |

| DB     | T <sub>PDH</sub> | PD Data Hold Time             | 25 | -              | ns |  |

Table 8 6 Bits RGB Interface Timing Characteristics

Page 15 of 24

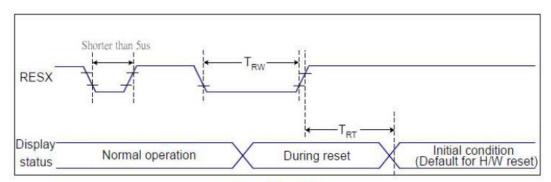

## 5.5 Reset Timing

Figure 7 Reset Timing

VDDI=1.65 to 3.3V, VDD=2.4 to 3.3V, AGND=DGND=0V, Ta=25 C

| Related Pins | Symbol | Parameter            | MIN                | MAX           | Unit |

|--------------|--------|----------------------|--------------------|---------------|------|

| RESX         | TRW    | Reset pulse duration | 10                 | 161           | us   |

|              | TOT    | Desetseed            | -                  | 5 (Note 1, 5) | ms   |

|              | TRT    | Reset cancel         | 120 (Note 1, 6, 7) |               | ms   |

**Table 9 Reset Timing**

#### Notes:

- The reset cancel includes also required time for loading ID bytes, VCOM setting and other settings from NVM (or similar device) to registers. This loading is done every time when there is HW reset cancel time (tRT) within 5 ms after a rising edge of RESX.

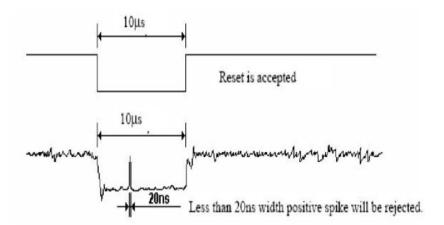

- 2. Spike due to an electrostatic discharge on RESX line does not cause irregular system reset according to the table below:

| RESX Pulse          | Action         |

|---------------------|----------------|

| Shorter than 5us    | Reset Rejected |

| Longer than 9us     | Reset          |

| Between 5us and 9us | Reset starts   |

3. During the Resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in Sleep Out –mode. The display remains the blank state in Sleep In –mode.) and then return to Default condition for Hardware Reset.

4. Spike Rejection also applies during a valid reset pulse as shown below:

- 5. When Reset applied during Sleep In Mode.

- 6. When Reset applied during Sleep Out Mode.

- 7. It is necessary to wait 5msec after releasing RESX before sending commands. Also Sleep Out command cannot be sent for 120msec.

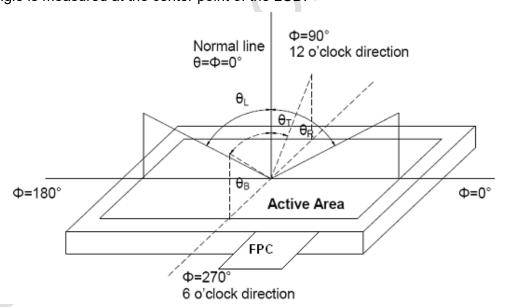

6 Optical Characteristics

| Item         |        | Symbol    | Condition    | Min   | Тур   | Max   | Unit              | Remark    |  |

|--------------|--------|-----------|--------------|-------|-------|-------|-------------------|-----------|--|

|              |        | θТ        |              | -     | 80    | -     |                   |           |  |

| View Angles  |        | θВ        | CR≧10        | =     | 80    | -     | Degree            | Note2,3   |  |

|              |        | θL        | CR≦10        | -     | 80    | ı     |                   | Note2,3   |  |

|              |        | θR        | -            | 80    | ı     |       |                   |           |  |

| Contrast R   | atio   | CR        | θ=0°         | -     | 600   | -     |                   | Note 3    |  |

| Response 1   | Timo   | $T_ON$    | <b>25</b> ℃  |       | 30    | _     | me                | Note 4    |  |

| Response     |        | $T_{OFF}$ | 25 0         |       | 30    | _     | ms                | Note 4    |  |

|              | White  | x         |              | 0.278 | 0.298 | 0.318 |                   | Note 1,5  |  |

|              | VVIIIC | у         | Backlight is | 0.294 | 0.314 | 0.334 |                   | 11010 1,0 |  |

|              | Red    | Х         |              |       |       |       |                   | Note 1,5  |  |

| Chromaticity | Rou    | у         |              |       |       |       |                   | 14010 1,0 |  |

| Omomation    | Green  | Х         | on           |       |       |       |                   | Note 1,5  |  |

|              | Oreen  | у         |              |       |       |       |                   | 14010 1,0 |  |

|              | Blue   | Х         |              |       |       |       |                   | Note 1,5  |  |

|              | Diac   | у         |              |       |       |       |                   | 14010 1,0 |  |

| Uniformi     | ty     | U         |              | 75    | 80    |       | %                 | Note 6    |  |

| Reflection i | atio   |           |              |       | 7%    |       |                   |           |  |

| Luminan      | се     | L         |              | 180   | 220   | -     | cd/m <sup>2</sup> | Note 7    |  |

## Test Conditions:

- 1.  $I_F$ = 20 mA, and the ambient temperature is 25  $^{\circ}$ C.

- 2. The test systems refer to Note 1 and Note 2.

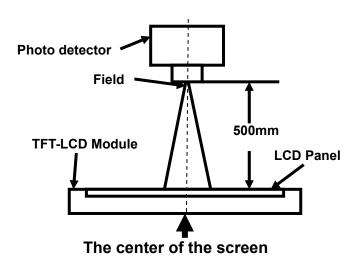

Note 1: Definition of optical measurement system.

The optical characteristics should be measured in dark room. After 5 Minutes operation, the optical properties are measured at the center point of the LCD screen. All input terminals LCD panel must be ground when measuring the center area of the panel.

Note 2: Definition of viewing angle range and measurement system. viewing angle is measured at the center point of the LCD.

Note 3: Definition of contrast ratio

Contrast ratio (CR) =  $\frac{\text{Luminance measured when LCD is on the "White" state}}{\text{Luminance measured when LCD is on the "Black" state}}$

"White state ": The state is that the LCD should drive by Vwhite.

"Black state": The state is that the LCD should drive by Vblack.

Vwhite: To be determined Vblack: To be determined.

The information contained herein is the exclusive property of Shenzhen Youri Technology Co.,Ltd,and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of Shenzhen Youri Technology Co.,Ltd

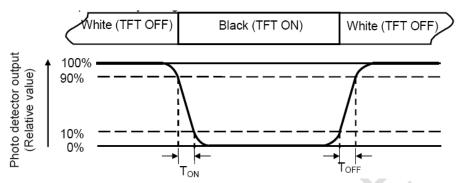

#### Note 4: Definition of Response time

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time  $(T_{ON})$  is the time between photo detector output intensity changed from 90% to 10%. And fall time  $(T_{OFF})$  is the time between photo detector output intensity changed from 10% to 90%.

Note 5: Definition of color chromaticity (CIE1931)

Color coordinates measured at center point of LCD.

Note 6: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (Refer Fig. 2). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U) = Lmin/Lmax

L-----Active area length W---- Active area width

Lmax: The measured Maximum luminance of all measurement position.

Lmin: The measured Minimum luminance of all measurement position.

Note 7: Definition of Luminance:

Measure the luminance of white state at center point.

## 7 Environmental / Reliability Test

| No | Test Item                                      | Condition                                                                                                    | Remarks                                                                                                   |

|----|------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 1  | High Temperature<br>Operation                  | 70℃, 120Hours                                                                                                | IEC60068-2-1:2007<br>GB2423.2-2008                                                                        |

| 2  | Low Temperature Operation                      | -20℃, 120 Hours                                                                                              | IEC60068-2-1:2007<br>GB2423.1-2008                                                                        |

| 3  | High Temperature<br>Storage                    | 80℃, 120 Hours                                                                                               | IEC60068-2-1:2007<br>GB2423.2-2008                                                                        |

| 4  | Low Temperature<br>Storage                     | -30℃, 120 Hours                                                                                              | IEC60068-2-1:2007<br>GB2423.1-2008                                                                        |

| 5  | Storage at High<br>Temperature and<br>Humidity | 50℃, 90%RH, 120 Hours                                                                                        | IEC60068-2-78 :2001<br>GB/T2423.3—2006                                                                    |

| 6  | Thermal Shock<br>(non-operation)               | -10℃,30min.<=> 60℃,30min.<br>10 Cycles                                                                       | Start with cold<br>temperature,<br>End with high<br>temperature,<br>IEC60068-2-14:1984,G<br>B2423.22-2002 |

| 7  | ESD                                            | Voltage: <u>+</u> 8KV<br>R:330 ohm,C:150pF<br>Air discharge,10 times                                         | IEC61000-4-2:2001<br>GB/T17626.2-2006                                                                     |

| 8  | Vibration Test                                 | 10 => 55 =>10 => 55 => 10 Hz,<br>within 1 minute;Amplitude:1.5mm.<br>15 minutes for each Direction ( X,Y,Z ) | IEC60068-2-6:1982<br>GB/T2423.10—1995                                                                     |

| 10 | Package Drop Test                              | Packed, 100CM free fall 6 sides, 1 corner, 3edges                                                            | IEC60068-2-32:1990<br>GB/T2423.8—1995                                                                     |

Note1: Ts is the temperature of panel's surface.

Note2: Ta is the ambient temperature of sample.

Note3: Before cosmetic and function test, the product must have enough recovery time, at least 2 hours at room temperature.

Note 4: In the standard condition, there shall be no practical problem that may affect the display function. After the reliability test, the product only guarantees operation, but don't guarantee all of the cosmetic specification.

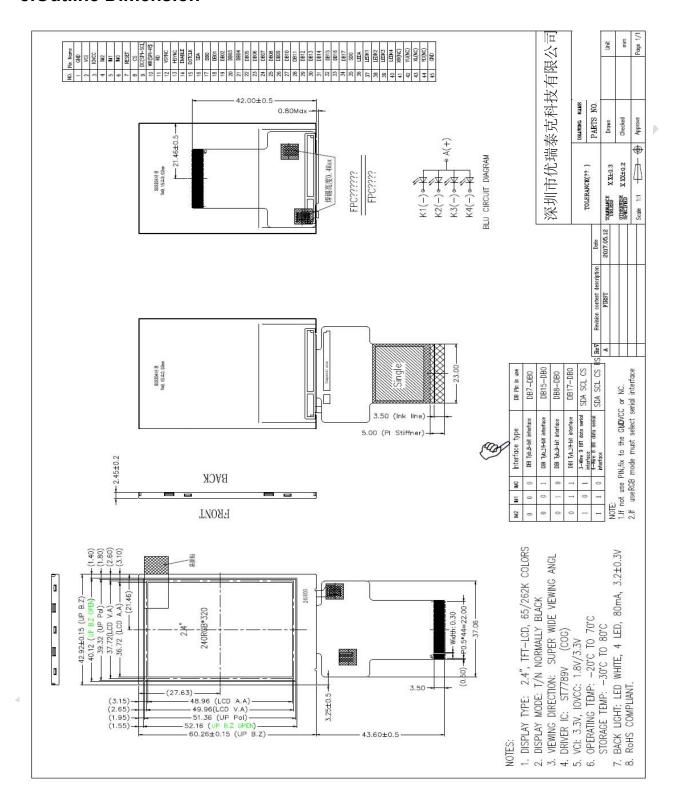

## **8.Outline Dimension**

## 9 Packing Drawing

**TBD**

## 10 Precautions for Use of LCD Modules

- a) Handling Precautions

- i. The display panel is made of glass. Do not subject it to a mechanical shock by dropping it from a high place, etc.

- ii. If the display panel is damaged and the liquid crystal substance inside it leaks out, be sure not to get any in your mouth, if the substance comes into contact with your skin or clothes, promptly wash it off using soap and water.

- iii. Do not apply excessive force to the display surface or the adjoining areas since this may cause the color tone to vary.

- iv. The polarizer covering the display surface of the LCD module is soft and easily scratched. Handle this polarizer carefully.

- v. If the display surface is contaMinated, breathe on the surface and gently wipe it with a soft dry cloth. If still not completely clear, moisten cloth with one of the following solvents:

- Isopropyl alcohol

- Ethyl alcohol

Solvents other than those mentioned above may damage the polarizer. Especially, do not use the following:

- Water

- Ketone

- Aromatic solvents

- vi. Do not attempt to disassemble the LCD Module.

- vii. If the logic circuit power is off, do not apply the input signals.

- viii. To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- 10.1.8.1 Be sure to ground the body when handling the LCD Modules.

- 10.1.8.2 Tools required for assembly, such as soldering irons, must be properly ground.

- 10.1.8.3 To reduce the amount of static electricity generated, do not conduct assembly and other work under dry conditions.

- 10.1.8.4 The LCD Module is coated with a film to protect the display surface. Be care when peeling off this protective film since static electricity may be generated.

- b) Storage precautions

- i. When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

- ii. The LCD modules should be stored under the storage temperature range. If the LCD modules will be stored for a long time, the recommend condition is:

Temperature :  $0^{\circ}$ C  $\sim 40^{\circ}$ C Relatively humidity:  $\leq 80\%$

- iii. The LCD modules should be stored in the room without acid, alkali and harmful gas.

- c) Transportation Precautions

- i. The LCD modules should be no falling and violent shocking during transportation, and also should avoid excessive press, water, damp and sunshine.